# University of Massachusetts Amherst ScholarWorks@UMass Amherst

Masters Theses 1911 - February 2014

Dissertations and Theses

January 2008

# Energy Efficient Adaptive Reed-Solomon Decoding System

Jonathan D. Allen *University of Massachusetts Amherst*, jallen@ecs.umass.edu

Follow this and additional works at: http://scholarworks.umass.edu/theses

Allen, Jonathan D., "Energy Efficient Adaptive Reed-Solomon Decoding System" (2008). *Masters Theses 1911 - February 2014*. 91. http://scholarworks.umass.edu/theses/91

This thesis is brought to you for free and open access by the Dissertations and Theses at ScholarWorks@UMass Amherst. It has been accepted for inclusion in Masters Theses 1911 - February 2014 by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

## ENERGY EFFICIENT ADAPTIVE REED-SOLOMON DECODING SYSTEM

A Thesis Presented

by

JONATHAN D. ALLEN

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE IN ELECTRICAL AND COMPUTER ENGINEERING

February 2008

Department of Electrical and Computer Engineering

## ENERGY EFFICIENT ADAPTIVE REED-SOLOMON DECODING SYSTEM

# A Thesis Presented

by

## JONATHAN D. ALLEN

| Approved as to style and content | by:                                               |

|----------------------------------|---------------------------------------------------|

|                                  |                                                   |

| Russell Tessier, Chair           |                                                   |

|                                  |                                                   |

| Dennis Goeckel, Member           |                                                   |

| Marinos Vouvakis, Member         |                                                   |

|                                  |                                                   |

|                                  |                                                   |

|                                  | C.V. Hollot, Department Head                      |

|                                  | Department of Electrical and Computer Engineering |

# CONTENTS

| LIST OF TABLES                                                                                      | vi  |

|-----------------------------------------------------------------------------------------------------|-----|

| LIST OF FIGURES                                                                                     | vii |

| CHAPTER                                                                                             |     |

| 1. INTRODUCTION                                                                                     | 1   |

| 2. BACKGROUND                                                                                       | 12  |

| 2.1. ECC and RS introduction                                                                        | 12  |

| 2.1.1. Reed-Solomon Codes                                                                           | 14  |

| 2.1.2. Galois Fields                                                                                | 15  |

| 2.1.3. Reed-Solomon Encoding Algorithm                                                              | 17  |

| 2.1.4. Reed-Solomon Decoding                                                                        | 23  |

| 2.2. Energy Consumption in FPGAs                                                                    | 31  |

| 2.3. Circuit Level Energy Reduction Methods                                                         | 32  |

| 2.3.1. Pipelining                                                                                   | 32  |

| 2.3.2. Clock Gating                                                                                 | 34  |

| 2.3.3. Memory Access Reduction Techniques                                                           | 37  |

| 2.4. Dynamic Reconfiguration                                                                        | 38  |

| 3. RELATED WORK                                                                                     | 40  |

| 3.1. Previous RS Works                                                                              | 40  |

| 3.1.1. A Low-Power Reed-Solomon Decoder for STM-16 Optical Communications                           | 40  |

| 3.1.2. Design of a Reed-Solomon Decoder using Partial Reconfiguration of XILIN FPGAs – A Case Study |     |

| 3.1.3. Architecture for Decoding Adaptive Reed-Solomon Codes with Variable Block Length             | 42  |

| 3.1.4. A Reed-Solomon Decoder with Efficient Recursive Cell Architecture for              |    |

|-------------------------------------------------------------------------------------------|----|

| DVD Applications                                                                          | 42 |

| 3.2. Previous FPGA Energy Reduction Works                                                 | 43 |

| 3.2.1. The Impact of Pipelining on Energy per Operation in Field-Programmable Gate Arrays | 43 |

| 3.2.2. Energy Efficient Signal Processing Using FPGAs                                     | 44 |

| 3.3. An Adaptive Errors-and-Erasures Reed-Solomon Decoder                                 | 45 |

| 3.4. Differences from Previous Work                                                       | 48 |

| 4. IMPLEMENTATION                                                                         | 50 |

| 4.1. Channel Fading Model                                                                 | 50 |

| 4.1.1. Goals and Requirements                                                             | 51 |

| 4.1.2. Simulation Flow                                                                    | 52 |

| 4.1.3. Model Details                                                                      | 54 |

| 4.1.4. Experiments                                                                        | 56 |

| 4.2. Hardware Optimizations                                                               | 58 |

| 4.2.1. Recoding                                                                           | 59 |

| 4.2.2. Pipelining                                                                         | 63 |

| 4.2.3. Memory Optimizations                                                               | 70 |

| 4.2.4. Clock Gating                                                                       | 72 |

| 5. CIRCUIT LEVEL OPTIMIZATIONS RESULTS AND ANALYSIS                                       | 76 |

| 5.1. Introduction                                                                         | 76 |

| 5.1.1. Previous Work                                                                      | 76 |

| 5.1.2. Quartus Synthesis Power Optimization                                               | 77 |

| 5.2. Recoding                                                                             | 79 |

| 5.3. Pipelining                                                                           | 82 |

| 5.3.1. Galois Field Multipliers                                                           | 82 |

| 5.3.2. Small-Scale Pipelining                                                             | 83 |

| 5.3.3. Global Pipelining                                                                  | 84 |

| 5.4. Memory Optimizations                    | 85 |

|----------------------------------------------|----|

| 5.5. Clock Gating                            | 87 |

| 5.6. Summary                                 | 91 |

| 6. RECONFIGURATION RATE ANALYSIS AND RESULTS | 92 |

| 6.1. New Reconfiguration Table               | 92 |

| 6.2. CER Analysis                            | 93 |

| 6.3. Energy Efficiency Results               | 95 |

| 6.4. Decoding Rate Results                   | 97 |

| 6.5. Summary                                 | 98 |

| REFERENCES                                   | 99 |

|                                              |    |

# LIST OF TABLES

| 2.1. Elements of GF(2 <sup>3</sup> ) shown in three different representations16                                         |

|-------------------------------------------------------------------------------------------------------------------------|

| 2.2. Roots of Key Polynomials                                                                                           |

| 3.1. Decoder Configurations, from [7]                                                                                   |

| 4.1. Clock Gating Parameters74                                                                                          |

| 5.1. Results Generated from Designs Developed in [7] using Quartus II, v7.177                                           |

| 5.2. Previous Work with Quartus Automated Power Optimization Results78                                                  |

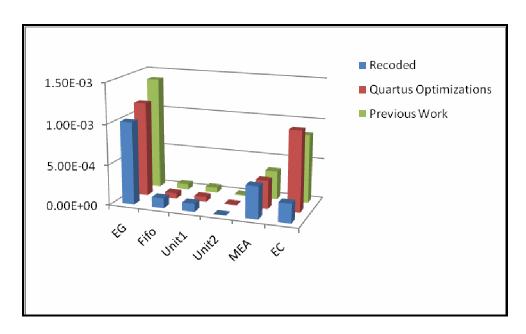

| 5.3. K239 Unit-by-unit Power Results                                                                                    |

| 5.4. Recoded Design Results, provides a new baseline for the following optimizations79                                  |

| 5.5. Functional Unit Energy Breakdown for Previous Work and Recoded80                                                   |

| 5.6. Cycle Counts for Decoding a Codeword                                                                               |

| 5.7. Pipelined Galois Field Multiplier Results                                                                          |

| 5.8. MEA Unit Comparison83                                                                                              |

| 5.9. Small-scale Pipelining Results                                                                                     |

| 5.10. Global Pipelining Results85                                                                                       |

| 5.11. Clock Cycles per codeword before and after global pipelining85                                                    |

| 5.12. Power Consumption results of Memory Buffering 20,400 bit memory86                                                 |

| 5.13. Power Consumption results of Memory Buffering 2040 bit memory86                                                   |

| 5.14. Results of Memory Optimizations                                                                                   |

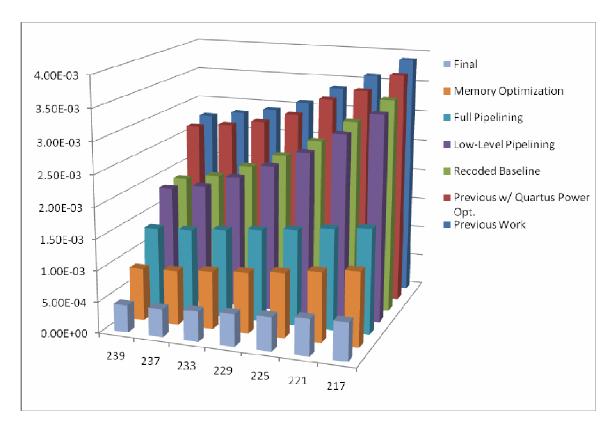

| 5.15. Final Results after Clock Gating                                                                                  |

| 5.16. Final Results, in Energy (J) per MB of Message Data Reduction in relation to Recoded baseline values (Table 5.4.) |

| 6.1. Configuration Table92                                                                                              |

# LIST OF FIGURES

| 1.1. Example of Glitching                                                                | 8  |

|------------------------------------------------------------------------------------------|----|

| 2.1. Typical Communication Scheme                                                        | 13 |

| 2.2. A General Reed-Solomon Encoder                                                      | 20 |

| 2.3. Rayleigh Fading Channel                                                             | 22 |

| 2.4. General Reed-Solomon Decoder Architecture                                           | 25 |

| 2.5. Clock Gating circuit                                                                | 34 |

| 2.6. Memory Buffering                                                                    | 37 |

| 2.7. Activity of Memory, original vs. buffered                                           | 38 |

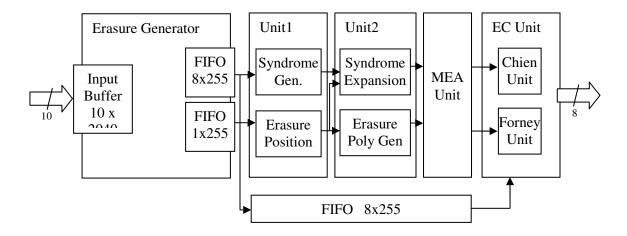

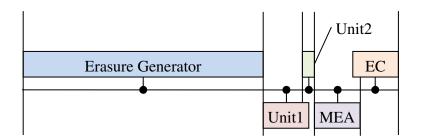

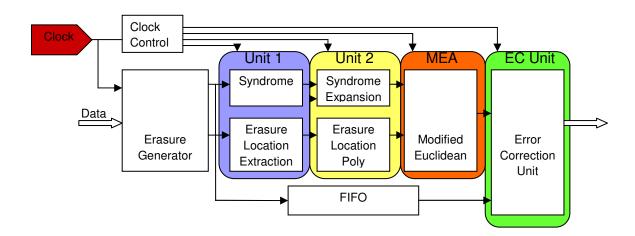

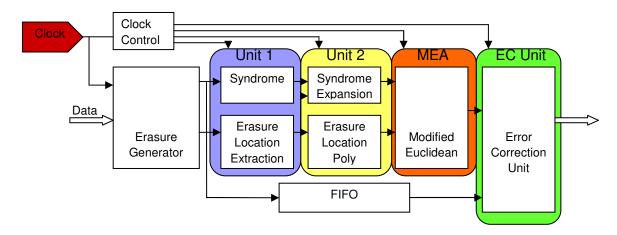

| 3.1. From [7], Architecture of an Adaptive errors-and-erasures Reed-Solomon Decod System | _  |

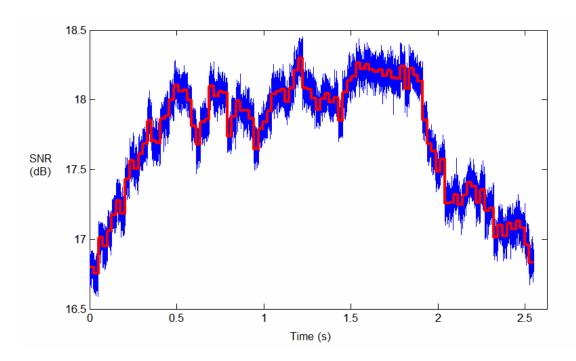

| 4.1. SNR due to Shadowing vs. Shadowing and Fading                                       | 52 |

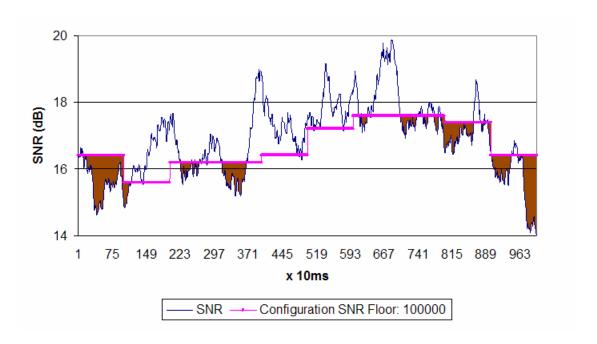

| 4.2. SNR variance during operation                                                       | 57 |

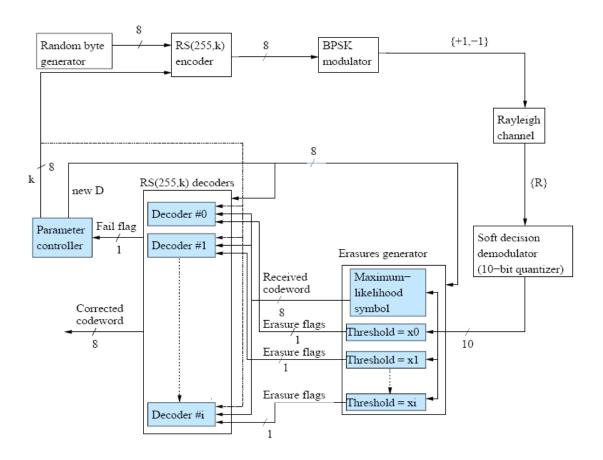

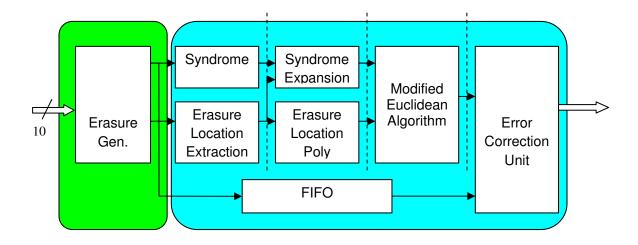

| 4.3. System Block Diagram                                                                | 58 |

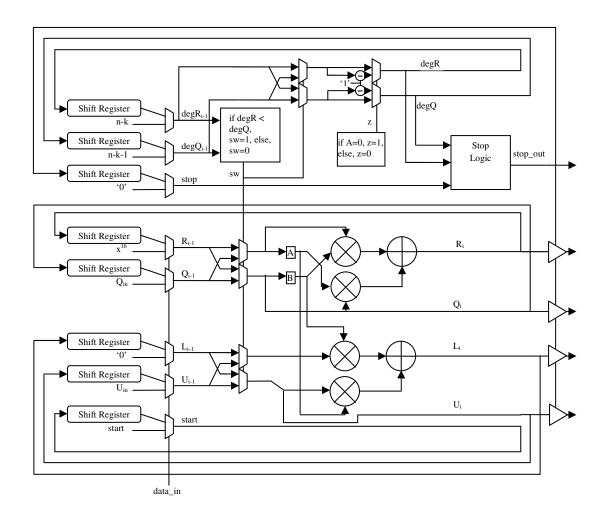

| 4.4. a) New MEA Structure b) Previous MEA structure [7].                                 | 61 |

| 4.5. Error Correction Unit                                                               | 63 |

| 4.6. MEA unit with 3-stage (above), and 5-stage (below) pipelining                       | 66 |

| 4.7. Time breakdown of the decoding process for an example of K=239 decoding             | 68 |

| 4.8. Timeline illustrating decoding of a codeword                                        | 68 |

| 4.9. Pipelining of Decoder Circuitry                                                     | 70 |

| 4.10. Example of Memory Buffering Logic                                                  | 71 |

| 4.11. Clock Gating Logic                                                                 | 74 |

| 4.12. Global Clocking Scheme                                                             | 75 |

| 5.1. K239 Unit by Unit Energy Consumption Breakdowns         | .80 |

|--------------------------------------------------------------|-----|

| 5.2. Global Clocking Scheme                                  | .88 |

| 5.3. Full Incremental Energy per Operation Results Breakdown | .89 |

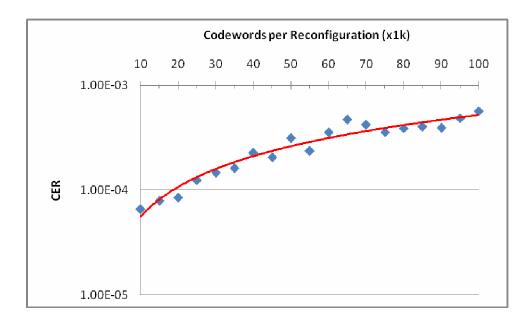

| 6.1. Graph of CER vs. Codewords per Reconfiguration          | .94 |

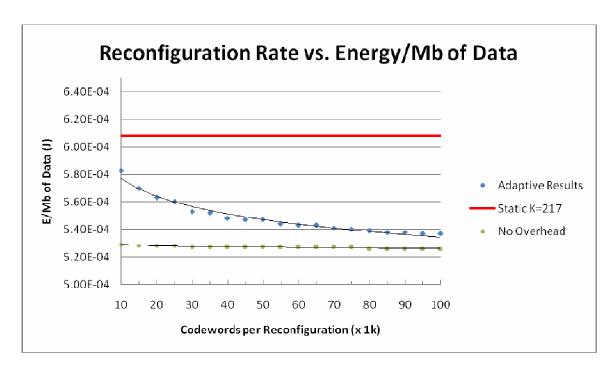

| 6.2. Energy per Megabit vs. Codewords per Reconfiguration    | .96 |

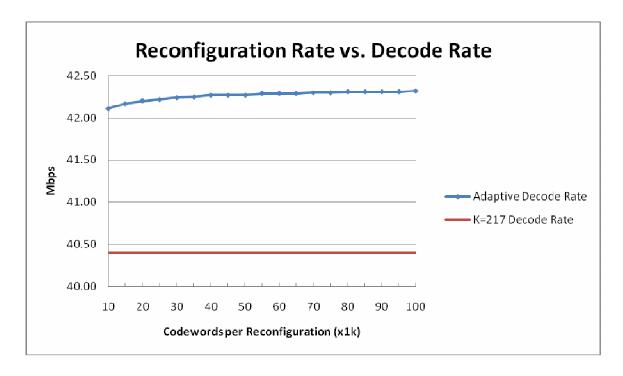

| 6.3. Reconfiguration Rate vs. Decode Rate                    | .97 |

#### CHAPTER 1

#### INTRODUCTION

In recent years the continued rise of portable data-devices such as cell phones, PDAs, and laptops has driven enormous growth in the area of wireless communications. Whenever data is sent over a wireless channel, it is subject to degradation due to multipath fading and noise. Depending on the amount of degradation, the effect can be a loss or corruption of the original data during transfer. In order to alleviate this problem and ensure the reliable transfer of data, the typical solution has been the use of an error correction coding scheme. This work will detail the implementation of a *low-energy* error correction coding (ECC) scheme, based on the widely used Reed-Solomon algorithm, which will be implemented using a field programmable gate array (FPGA) device. FPGAs have been adopted for use in wireless communication and digital signal processing (DSP) applications due to their ease of use when compared to traditional DSP microcontrollers, high performance characteristics, and inherent configurability. Despite these benefits, much work remains to be done in order for these devices to truly be adopted for use in wireless devices, as current FPGAs are not naturally low-energy devices. This work will examine how to leverage the specialization and configurability of these devices in order to achieve low energy consumption characteristics while maintaining high levels of performance. This work is primarily aimed at systems which already include an FPGA for computation, as the performance of our algorithm implemented on an FPGA will not be able to outperform an ASIC implementation in terms of energy consumption. However, there are situations where incorporating a ReedSolomon decoding system into the functionality of an FPGA based system may be desirable, and the configurability of the FPGA allows for the processing unit to perform multiple operations simultaneously. In this case, it is much more desirable to implement the decoder in the pre-existing FPGA as opposed to incorporating a Reed-Solomon ASIC into the design.

The main contribution of this work is the development and analysis of an FPGA based Adaptive Reed-Solomon errors-and-erasures decoding system which is optimized to minimize energy consumption characteristics. This work is based on an earlier project [15][7], which has been modified to ensure low-energy operation through the use of several circuit-level energy optimization techniques and in addition to a new analysis of a scheduling approach for dynamic reconfiguration. The end result of the energy optimization is a reduction in system energy consumption of more than 70% compared to previous work.

The origin of ECC schemes dates back to the work of Shannon in 1948. His work [1][3][11] demonstrated that by properly encoding information before transferring over a lossy channel, the errors which are introduced in the channel can be reduced to any desired level without a severe decrease in transmission rate. Since then researchers have developed various error correction schemes. One of the most widely used of these schemes is Reed-Solomon coding [1][2]. Reed-Solomon coding has been used in systems ranging from CD players [4][23] (to correct errors introduced by dust in the optical drive) to NASA's wireless deep-space communications [24]. Reed-Solomon coding is what's known as a block coding scheme, under which fixed length blocks of data are encoded with a fixed amount of parity information. Other ECC schemes include Viterbi coding

[5], along with more recent schemes such as Turbocoding [6]. Traditionally, these algorithms have been implemented using DSP microcontrollers, which are based on microprocessors but specialized to allow for better signal processing performance. Recent work [25][26]has examined using FPGAs for these applications, as they provide similar performance characteristics while allowing for a much more customized design, with simplified and quicker development. FPGAs are customizable logic devices, which have seen more and more use in consumer and industrial electronics in recent years, are an alternative to traditional microprocessors and DSP devices. FPGAs are attractive devices to developers in need of specific solutions, as their configurability allows designers to tailor the device to provide the specific functionality necessary for a particular application. In addition, because the functionality is coded into the hardware of the device, mapping an application to an FPGA usually allows for an optimized, high-speed implementation, and allows to designer to customize the application at a much lower level than if he or she was using a general-purpose microprocessor.

Historically, the designers of ECC systems have focused on providing the best possible performance while maintaining the desired quality of service (QoS). Typically the limiting factor in these systems has been the data transfer rate, as all communication channels pose restrictions on their maximum bandwidth. However, with the continued growth of wireless systems, battery-powered devices of all types, power and energy consumption have become increasingly important design constraints.

The majority of mobile devices are no longer stand-alone devices. Increasingly, these devices are required to have extensive connectivity options, which means a need for wireless communications. If one examines a recently developed device such as Apple's

Iphone[27], we can see the need for not just one, but multiple wireless communication methods, from BlueTooth to 802.11 b/g wireless to cellular phone service and data transfer. These devices are constrained by the amount of energy which can be contained in their batteries, which introduces new design challenges for developers of these devices.

The work detailed in this document includes the development and analysis of a low-energy ECC decoding system, implemented on an Altera FPGA. It draws on previous works on ECC coding, and low power and energy FPGA design. The starting point for this is the work of Lilian Atieno [7], who developed an FPGA based adaptive errors-and-erasures Reed-Solomon decoding system. Her system was designed to adapt dynamically to changes in the noise level of the communication channel in order to provide maximum data-rates and reduced power consumption when compared to a static implementation of the decoding circuitry. If the channel is noisy, leading to increased error rates, a larger, more power-hungry decoder is swapped into the FPGA in order to keep the error rate below the required level. When there is less noise in the channel, a smaller, faster, and less power-hungry decoder is swapped in. The main metric of success for this previous work was decoding speed, with the secondary metric being power consumption.

Building on this previous work, this project adapts the previous design to minimize the amount of energy required to decode a particular amount of message data. Several modifications are made to both the structure of the design at the circuit level, and to the overall system functionality. An additional contribution of this work is the development of a more accurate channel noise and fading model, to get a better understanding of the real-world performance characteristics that could be expected.

The methods used in this work fall into two basic categories, application specific optimizations, and application independent, circuit level optimizations.

The application specific methods used during this work include:

## 1) Efficient Implementation of Application Primitives

The Reed-Solomon decoding application requires a multitude of specialized functional units to decode and correct errors in message data coming from a noisy channel. The fundamental units are Galois Field multipliers and Galois Field adders, which perform the most basic operations within the decoder. Larger units include the syndrome generation unit, the syndrome expansion unit, and the modified Euclidean algorithm block. Some of these units can be implemented several different ways in the FPGA hardware, so it is important that care be taken to ensure not only that the most efficient structure is used (in terms of energy consumption), but also that the desired structures are mapped as expected to the FPGA fabric. The development of a pipelined Galois field multiplier will be specifically documented in Chapter 4, along with the comparison of different structural implementations of the modified Euclidean algorithm block.

#### 2) Adaptive System Design and Scheduling

The previous system makes use of a reconfiguration scheme designed to allow the functionality of the decoder to adapt to changing channel conditions in order to maintain the maximum possible decoding rate. For this work, the goal was to adapt to changing channel conditions to ensure the lowest energy consumption possible while maintaining a

fixed minimum codeword error rate (CER). Several changes to the overall system functionality were made. The previous system used several RS decoders in parallel, while maintaining the desired CER and decoding rate. This approach is inherently wasteful in terms of energy, since the result from only one decoder is ultimately used. Given that we are primarily concerned with energy, only single decoder versions are considered. This has a positive side-effect of reducing the total number of reconfigurations needed, as there are only seven different configurations as opposed to the previous system's twenty. The negative side effect is a slight reduction in decoding speed. This will be described in detail in Chapter 4.

The second change from the previous work is a more accurate channel model to evaluate the system's overall performance. The previous approach was designed to operate in a Rayleigh fading channel environment, with average SNRs varying from around 13 to 21dB. However, the model used to evaluate the system performance was not time-dependant, allowing for unrealistic changes in signal quality in short amounts of time. In order to better evaluate the performance of the system in a real-world situation, a time-dependant Rayleigh fading channel model was developed, which has several benefits over the previous model. Time dependency allows for evaluation of optimal reconfiguration rates answering the question, "How long should we wait before evaluating whether to reconfigure the system?" In addition, we evaluate the effects of differing reconfiguration rates on both the energy consumption characteristics and errorrate performance. The new model is used to answer several questions: first, what is the effect of the rate of reconfiguration on energy consumption, and second, what is the

effect of varying the rate of reconfiguration on the codeword error rate? This analysis is described in detail in Chapter 4, with final results shown in Chapter 5.

As mentioned above, application independent optimization methods were also used to reduce decoder energy consumption in the FPGA device. These methods are applicable to any design mapped to an FPGA, and have been shown in previous work to reduce energy consumption characteristics. Each of these methods was applied to the decoder circuitry at the highest level, and represent design choices which can be made by the designer of the application in order to reduce dynamic energy consumption. This is in contrast to algorithmic modifications which are automatically performed at lower levels by the CAD software used in FPGA development. It has been shown that higher level optimizations lead to the greatest possible benefit.

The methods used are detailed briefly below, and in full detail in Chapter 2.

1) Pipelining

Pipelining has been shown to reduce energy consumption in digital circuits, including FPGAs [8]. Pipelining allows for lower energy consumption by reducing the propagation of glitches through the circuitry. Glitches are defined as spurious transitions in the circuitry caused by timing mismatches. Figure 1.1 below illustrates how mismatched logic delays can cause spurious transitions.

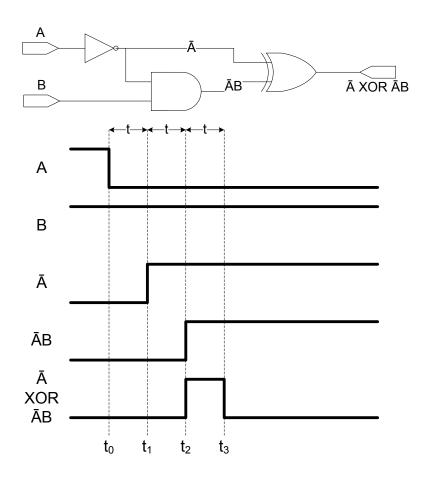

Figure 1.1. Example of Glitching

Assuming all of the gates have a delay of t, at  $t_0$ , input A goes from high to low. After one time unit, A inverse reflects this change. After another time unit, inverse A has caused a change in the output, even though the output of the AND gate hasn't propagated. After another time unit, the correct result is shown at the output. However, as the output went high briefly, this is an example of a glitch cause by mismatched logic depths, and in fact this glitch caused two separate spurious signal transitions.

As each signal transition in a digital device dissipates energy, minimizing the amount of unneeded transitions due to differing logic timing characteristics and reducing the distance these glitches are allowed to propagate is important in reducing energy consumption. If the output of the above circuit was fed onto a long communication line in the FPGA, the amount of energy dissipated by the glitch could be very large.

Pipelining is accomplished by inserting registers throughout the design, which effectively cuts off the propagation of glitches beyond the register. FPGAs have a configurable internal communication network made up of many long, high-capacitance wires, which dissipate significant amounts of energy. Considering their energy dissipation characteristics, reducing the number of transitions on these lines is paramount. In addition, pipelining allows for the hardware resources to be better utilized by allowing for greater levels of parallelism to be built into the application. This improves energy characteristics by preventing logic from being idle and thus dissipating energy without a purpose.

## 2) Clock Gating

Clock gating of digital circuits is another technique which has been shown to reduce energy consumption both in ASICs [9] and FPGAs [10]. The essential idea is that some parts of a design may not be needed for part of its operation, i.e. this portion of the circuit on this clock cycle generates an output value which is not needed by another portion of the circuit. If this is the case, these design features can have their clock suppressed (gated) so that the clock is not propagated to them when their results are unneeded, ensuring that they do not dissipate energy. Given that the RS system contains many individual functional blocks which are not needed at all times, clock gating these units so that they are only active when needed provides the opportunity to save large amounts of energy.

## 3) Efficient Structuring of Embedded Memories

As memory units dissipate energy on every read or write operation, reducing the overall number of accesses reduces the overall energy consumption of the design. A method was developed to combine data into large blocks for each read and write operation to reduce the number of required memory accesses. This technique allows for a more efficient use of clock gating for internal FPGA memory blocks and allows the memory to be inactive for a larger percentage of the time. While this can increase the energy required to perform an individual read or write, by greatly reducing the number of necessary reads and writes, energy consumption can be reduced. In many ways, these units work as small caches, preloading the data which will be needed for the next several clock cycles in order to allow the memory to maintain a lower activity rate.

Overall, applying these circuit level techniques resulted in a net reduction in the energy required to decode a megabit of data by 70%. The specific areas where each optimization was performed are detailed in Chapter 4, while the numerical benefits are shown in Chapter 5.

The rest of this document is structured as follows. Chapter 2 provides background information on the Reed-Solomon algorithm, a discussion of the sources of energy consumption in FPGA circuitry, and a detailed look at the energy reduction techniques which were used in this work.

Chapter 3 details related works in FPGA energy reduction and Reed-Solomon decoder implementations.

Chapter 4 details where the aforementioned techniques were used in the development of the decoding system, while also describing in detail the methodology that was used for these techniques, along with a detailed description of the new channel model, and how it was used to evaluate the performance of the system.

Chapter 5 provides numerical results for each individual optimization technique, while also providing overall system performance data.

Chapter 6 provides numerical results for the reconfiguration scheduling and analysis part of this work.

#### CHAPTER 2

#### **BACKGROUND**

## 2.1) ECC and RS introduction

All methods of digital communication are subject to some sort of noise or interference, whether the medium of communication is a physical link or a wireless one. In physical systems, noise can be introduced by the electromagnetic fields generated by the surrounding circuitry and components, by errors in data storage, or even physical phenomena such as a particle of dust getting in the way of a laser beam reading data from an optical storage device. In wireless channels, errors can be created by interference from other wireless signals, interference caused by the signal passing through a building, or fading caused by differing propagational paths of the wireless signal. The main challenge in digital communications has become how to deal with these unavoidable errors in an efficient way, so as to prevent data loss without causing undue overhead.

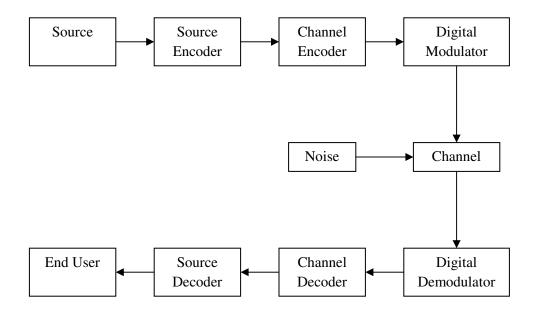

The work of Shannon [11] demonstrated that even though communication channels are subject to noise and errors, if some amount of redundancy is encoded into the signal, errors can be accounted for and corrected at the receiving end. This is the fundamental principle of error-correction coding schemes, and has led to the development of various encoding schemes, including Reed-Solomon coding. A typical communication scheme that meets this criterion can be modeled as seen in Figure 2.1.

Figure 2.1. Typical Communication Scheme

The source represents the origin of the data to be sent, and can be a physical storage device such as a CD, DVD, or Magneto-Optical recording device with the data already in digital form, or an analog signal such as a voice or music sample. The source is first encoded into digital form if it wasn't already in such a form. The output of the source encoder must be a sequence of binary digits representing the data. How this encoding is performed is determined by the needs of the system, and is irrelevant to the communication methodology.

The data stream is then sent through the channel encoder, where the ECC encoding is performed. This unit takes the incoming data and adds redundancy via whichever ECC scheme is in use. In this work, a Reed-Solomon encoding device is used.

The encoded data is then sent to the digital modulator, which takes the digital signal and creates an analog waveform to be transmitted over the communication channel.

As the analog signal is transmitted over the channel, it is subject to noise, which distorts the original signal so that what is received at the other end is not identical to the signal which was sent. Noise is the source of the errors, which need to be corrected.

When the signal is received at the end of the channel, it is demodulated back into digital form by the demodulator. This process is the exact inverse of the modulation process, and the end result is again a stream of binary data. However, as mentioned above, the signal has changed due to noise during transmission, and so in most cases, the binary sequence output from the demodulator is not identical to the one which was originally presented to the modulator.

This sequence is then fed into the channel decoder, which attempts to decode the signal in a way that recovers all of the original data, correcting any errors which were introduced during transmission. This is made possible by the redundancy which was added to the signal during encoding. In this work, the decoding system is the main application of interest, and represents a Reed-Solomon decoding system.

After the errors have been corrected to the decoder's best ability, the data is transformed into the required format, for example, in a phone conversation, the binary stream is converted back into an analog signal to be output to the receiver's speaker.

#### 2.1.1) Reed-Solomon Codes

Reed-Solomon codes were first introduced by Irving Reeds and Gus Solomon in 1960, in a paper entitled "Polynomial codes over certain finite fields" [2]. Since their

inception, RS codes have been one of the most widely used ECC schemes, mainly because the coding scheme allows for efficient correction of both burst and random errors. Reed-Solomon coding is known as a non-linear, block based coding scheme. RS is a block scheme because it encodes blocks of a specific amount of data individually, as opposed to operating on the entire data stream as a whole. RS codes are based on finite field arithmetic, known as Galois fields. These fields are mathematical constructs in which any operation on one data element results in another element in a constrained field. The general operation can be described as follows; a predetermined sized block of data (k bytes) is encoded so that the result is a data block of size n, where n>k. This size n block contains the k original data bytes, along with n-k parity bytes, representing the redundancy in the signal, for transmission over the noisy channel. Within the block, the RS algorithm works on multiple bits of data at a time, typically a byte. Each byte is a symbol, and the nature of the RS algorithm allows for the correction of whole symbols, as opposed to correcting individual bits. This means that the RS decoder can correct a symbol with 8 bit errors as well as a symbol with 1 bit in error. This is the particular characteristic which allows RS codes to be effective at correcting burst errors in addition to random errors.

#### 2.1.2) Galois Fields

As mentioned above, the RS coding scheme uses abstract mathematical constructs known as Galois Fields. Each field contains a finite number of elements, and operations on elements in the field can only produce a result within the same field. The benefits of this kind of arithmetic include not having to deal with overflows and carries. Galois fields

are defined as  $GF(X^Y)$ , where  $X^Y$  equals the total number of elements in the field. For RS codes, X must be a prime positive integer, and Y must be an integer greater than or equal to 3. Y also determines the number of bits operated on simultaneously, so in the case of our RS system, Y will be equal to 8. X will be defined as 2 as this is a common value, and lends itself well to digital implementations.

As an example, Table 2.1 shows the elements of the Galois field  $GF(2^3)$ . Elements of the Galois field are generated from the 'primitive polynomial' p(x), in this case,  $p(x)=1+x+x^3$ . When doing calculations in digital circuitry, the elements of each table entry are typically represented by bit values, instead of polynomial or power representations.

| Power Representation | Polynomial Representation | 3-Tuple Representation |

|----------------------|---------------------------|------------------------|

| -∞                   | 0                         | 0 0 0                  |

| 0                    | 1                         | 0 0 1                  |

| α                    | α                         | 0 1 0                  |

| $\alpha^2$           | $\alpha^2$                | 1 0 0                  |

| $\alpha^3$           | α + 1                     | 0 1 1                  |

| $\alpha^4$           | $\alpha^2 + \alpha$       | 1 1 0                  |

| $\alpha^5$           | $\alpha^2 + \alpha + 1$   | 111                    |

| $\alpha^6$           | $\alpha^2 + 1$            | 1 0 1                  |

Table 2.1. Elements of GF(2<sup>3</sup>) shown in three different representations

Arithmetic operations performed within a Galois field are performed differently than when using typical arithmetic. The two operations used in the RS system are GF adds and GF multiplications. GF addition is performed in binary systems by XORing the corresponding bits of the codeword, which represent the coefficients of the polynomial. For example:

$$\alpha^6 + \alpha^4 = [101] + [110] = [011] = \alpha^3$$

GF multiplication is performed by adding the indices of the polynomial, for example:

$$\alpha^3 * \alpha^2 = \alpha^{2+3} = \alpha^5$$

In binary form, this operation is a modulo 2 sum of partial products, and which requires specialized multiplier circuitry. The circuitry will be described in detail in Chapter 4.

## 2.1.3) Reed-Solomon Encoding Algorithm

This section will provide an overview of the Reed-Solomon encoding and decoding algorithms, focusing on the mathematical description, while Chapter 3 will provide a look at how the decoding algorithm was previously implemented in hardware.

As mentioned above, Reed-Solomon codes operate on GF of the order  $q=p^m$ , where m is a positive integer greater than or equal to 3. Typically, the value of p is 2, and a typical value of q is 256. For this example, the assumed values will be p=2 and q=8, because the math becomes very complex as q scales upward. Our experimental implementation utilizes a q value of 256. Each GF is generated from a primitive polynomial of  $p(x)=1+x+x^3$ .

The three columns in Table 2.1 illustrate different ways of representing the same data. If this particular GF was to be implemented in circuitry, 3-tuple representation

would be used, given its binary representation. All of the operations in the RS algorithm operate within this constrained field, meaning that any operation on data within the field will result in another entry within the field.

The encoding process is accomplished by taking in a k-bit block of data, and generating n-k parity bits to append to the original data for transfer. RS encoding makes use of a generator polynomial. The encoder generates the parity symbols by dividing the data by the generator polynomial, with the remainder being the parity bits.

An example of RS encoding follows. For this example, the code used is RS(7,3) operating on the  $GF(2^3)$ , the elements of which are shown in Table 2.1. This implies that the encoder operates on 3-bit symbols, 3 of which will be used to generate 4 3-bit parity values, for a total message length of 7 3-bit symbols. A summary of the parameters is shown below.

$$n=7, k=3$$

$$t=(7-3)/2=2$$

N represents the total codeword length in symbols, while K represents the number of data symbols in each codeword. T represents the error correcting capability of the coding scheme. In this case, an errors-only RS(7,3) decoder can correct 2 erroneous symbols in the codeword, while and errors-and-erasures version of the same decoder can correct 2t=4 erroneous symbols. The difference between an errors-only and an errors and erasures decoder will be discussed in Chapter 3.

Suppose that the message below is to be encoded:

As one can see from examining Table 2.1., this data can be represented in both polynomial form, as:

$$u(x) = \alpha^3 x^2 + \alpha^3 x^1 + \alpha^1 x$$

and in power form, as:

$$u = \alpha^3 \alpha^3 \alpha^1$$

The value of x in the polynomial form represents the position of the symbol in the block.

To determine the parity bits of the signal, a *generator polynomial* is used. It's general form is:

$$g(x) = (x + \alpha^{0})(x + \alpha^{1}) + \dots + (x + \alpha^{2t-1})$$

Given that for this example, t=2, the generator polynomial used is:

$$g(x) = (x + \alpha^0)(x + \alpha^1)(x + \alpha^2)(x + \alpha^3)$$

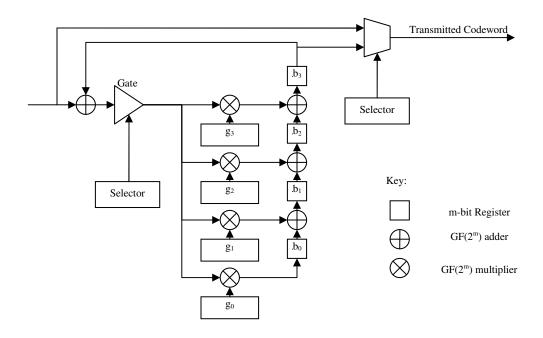

This can be expanded to  $g(x) = \alpha^6 + \alpha^5 x + \alpha^5 x^2 + \alpha^2 x^3 + x^4$ , so the coefficients of g are  $g_0 = \alpha^6$ ,  $g_1 = \alpha^5$ ,  $g_2 = \alpha^5$ ,  $g_3 = \alpha^2$ . A simplified architecture for the encoder is illustrated below.

Figure 2.2. A general Reed-Solomon Encoder

The encoder uses the roots of g(x), along with a selection signal. This signal ensures that for the first m clock cycles, the input data is propagated to the output, followed by the propagation of the calculated parity symbols. An example using  $GF(2^3)$  is detailed below.

- Clock Cycle 1: The first message symbol 011 (or  $\alpha^3$ ) is sent into the encoder. The symbol is multiplied by each of the generator coefficients, and added to the previous data in registers  $b_0, b_1, b_2, b_3$ , which in this case, since this is the initial cycle, are all equal to 000. The resulting register values are:

- o  $b_0 = \alpha^3 * \alpha^6 = \alpha^9$ , which simplifies to  $\alpha^2$

o

$$b_1 = \alpha^3 * \alpha^5 + 000 = \alpha^8$$

, which simplifies to  $\alpha^1$

$$b_2 = \alpha^3 * \alpha^5 + 000 = \alpha^1$$

$$b_3 = \alpha^3 * \alpha^2 + 000 = \alpha^5$$

Clock Cycle 2: The second message symbol, 011 ( $\alpha^3$ ) is sent into the decoder. It is XORed with the value of b<sub>3</sub>, which is 111 ( $\alpha^5$ ) resulting in 101 ( $\alpha^2$ ). This value is multiplied by the generator coefficients, resulting in register values of:

$$b_0 = \alpha^2 * \alpha^6 = \alpha^9 = \alpha^1$$

$$b_1 = \alpha^2 * \alpha^5 + \alpha^2 = \alpha^6$$

$$b_2 = \alpha^2 * \alpha^5 + \alpha^1 = \alpha^3$$

$$b_3 = \alpha^2 * \alpha^2 + \alpha^1 = \alpha^2$$

Clock Cycle 3: The third message symbol, 010 ( $\alpha^1$ ) is fed into the decoder. It is XORed with the value of  $b_3$ ,  $\alpha^2$ , resulting in  $\alpha^4$ . The end results in the registers are:

$$\circ b_0 = \alpha^4 * \alpha^6 = \alpha^3$$

$$\circ \quad b_1 = \alpha^4 * \alpha^5 + \alpha^1 = \alpha^4$$

$$b_2 = \alpha^4 * \alpha^5 + \alpha^6 = \alpha^0$$

$$b_3 = \alpha^4 * \alpha^2 + \alpha^3 = \alpha^4$$

Clock Cycle 4-7: As the counter is now equal to 4, the data in registers b<sub>0</sub>, b<sub>1</sub>, and

b<sub>2</sub> contain the parity data to be appended to the signal. The gate is disconnected,

and the data is allowed to propagate out of the circuit.

The final message sent to the channel is [011,011,010,110,001,110,011]. The first 3 tuples are the original data, and the trailing four are the parity symbols. This binary string is modulated into an analog form. A typical modulation scheme is the Binary Phase Shift Key (BPSK) modulator, which transforms the data into a waveform, with 1s becoming -1s, and 0s becoming +1s. This signal is transmitted over the channel, and is subject to noise in the form of Rayleigh channel fading, and additive Gaussian white noise (AGWN).

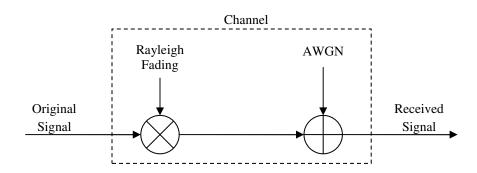

Figure 2.3. Rayleigh Fading Channel

The above diagram illustrates a typical Rayleigh fading channel. Rayleigh fading occurs because of the nature of a wireless transmitting environment. Signals in an environment such as this scatter off of physical objects such as walls and the result is that there are multiple paths from the transmitter to the receiver, resulting in different amounts of signal power coming to the antenna from different directions. In addition, electromagnetic interference also affects the signal while in transit. The resulting effect can be described mathematically as:

$$y_r = y_s * f + n$$

where  $y_s$  represents the signal as sent,  $y_r$  represents the signal as received, f represents the Rayleigh fading gain of the channel, and n represents the AWGN during transmission. Typically these parameters change over the course of the transmission of the codeword, so this can be better modeled on a bit by bit basis as:

$$y_r^i = y_s^i * f^i + n^i$$

where i stands for the  $i^{th}$  bit of the transmitted sequence.

## 2.1.4) Reed-Solomon Decoding

When the signal from the encoder is modulated and passed through the channel, it is subject to both Rayleigh fading and AGWN, and thus the signal is not the clean -1 and +1 signs when it is received. The demodulator takes in this analog signal, and outputs floating point estimations of each bit's value. There are two ways to perform the decoding of this modified data, hard-decision decoding, and soft-decision decoding. Hard decision decoding yields an error-only RS decoder, and functions by determining that any signal received which is below 0 becomes a -1, and above zero becomes a +1. While this is usually correct, in the case where a large amount of noise was injected into the signal, these hard decisions may be incorrect. Consider for example a symbol which is received and demodulated into the values {.0675, -.0238, -.8905}. Using hard decision demodulation, this would become {+1, -1, -1}. However, the second bit is so close to 0 that it could conceivably have been either a +1 or -1 originally. When using hard-decision demodulation, the decoder has no way of knowing that this bit is unreliable, information which could aid in the decoding process.

Soft decision demodulation uses an *erasure generator* to signal the decoder when particular symbols are unreliable. The decoder still receives streams of the "most likely" symbols, but also receives a stream of flags indicating when a particular symbol is unreliable. The erasure generator takes in a symbol at a time, and generates two possible values, the most likely symbol (MLS), and 2<sup>nd</sup> MLS. The second MLS is determined by negating the bit with the lowest absolute amplitude, as this is the least reliable bit. It then calculates the difference between the two different symbols, the MLS and the 2<sup>nd</sup> MLS, and compares this to a pre-set threshold value. The actual function to determine whether to assert the erasure flag is detailed below.

The receiver receives y, representing the amplitudes of the received data from the channel. It then calculates the most likely symbol, or MLS, based on the fact that y was received. The possible symbols are denoted as  $s_0, s_1, ...s_{n-1}$ . This function is denoted as:

$$max_v f(y^j \backslash s_v)$$

The erasure flag is asserted for a particular symbol if and only if:

$$\frac{\max_{v} f(y^{j} \setminus s_{v})}{\sum_{i=0}^{n-1} f(y \setminus s_{i})} = 1 - T$$

where  $s_{\nu}$  represents the MLS, and the bottom term represents the total conditional probability of  $s_{\nu}$  given that  $y^{j}$  was received.

The principal benefit of using a soft decision, errors-and-erasures version of an RS decoder is that the amount of errors that can be corrected per codeword is increased. The amount of errors that can be corrected by a hard decision decoder is t, while a soft-decision decoder can correct 2t erroneous symbols per codeword.

Figure 2.4 shows the general structure of an errors-and-erasures RS decoder. This decoder receives the stream of estimated data and a stream of erasure flags from the erasure generator, and attempts to correct any errors.

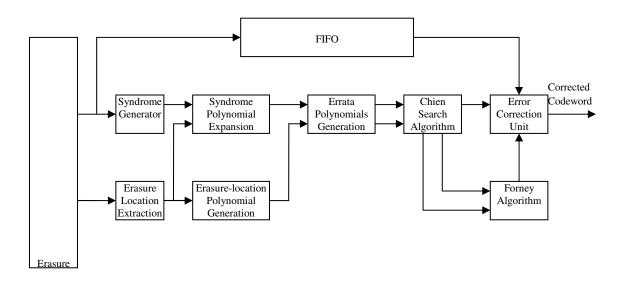

Figure 2.4. General Reed-Solomon Decoder Architecture

This next section will contain an example of RS soft-decision decoding, following from the encoding example. Each block's operation will be discussed along with the example.

## 1) Syndrome Generation Block

The function of the syndrome generation block is to divide the received codeword by the generator polynomial. As mentioned earlier, any valid codeword will be exactly divisible by the generator polynomial. If there is a remainder, one can assume that there are errors in the codeword. The typical method of performing this division is to substitute

all of the 2t roots of the generator poly into the received polynomial, generating 2t syndrome coefficients. This is known as the syndrome polynomial. If all of the coefficients are zero, then there are no errors in the codeword, and error correction can be bypassed.

Given the example from the encoding section, the received codeword should be u(x) = [011,011,010,110,001,110,011].

Let us assume that instead, the received sequence is:

$$u(x) = [011, \mathbf{010}, \mathbf{100}, 110, 001, 110, 011].$$

The polynomial representation of this sequence is:

$$u(x) = \alpha^3 x^6 + \alpha^1 x^5 + \alpha^2 x^4 + \alpha^4 x^3 + \alpha^0 x^2 + \alpha^4 x + \alpha^3$$

Two errors were introduced during the transmission of the signal over the channel, one in the second symbol, and one in the third. The syndrome generation unit substitutes all of the roots of the generator polynomial into the above equation, resulting in:

$$s(x) = \alpha^4 x^3 + \alpha^2 x^2 + \alpha^6 x + \alpha^5$$

#### 2) Erasure Location Extraction

This block receives the stream of erasure flags from the erasure generator, and expands them into a polynomial for use in calculating the locations of errors in the codeword. As erasure generation is not 100% accurate, let us assume that only the second symbol was flagged as being unreliable, and the third symbol, which also has an error, was missed.

When the second symbol arrives at the syndrome generation block, an erasure flag arrives at the erasure location extraction block. This block then performs the following calculation:

$$t = \alpha^{n-1}$$

$$t = \alpha^{7-2}$$

$$t = \alpha^5$$

The resulting polynomial is the sum of all of the results for every erasure flag plus 1. Since in this case there is only a single erasure flag, the resultant polynomial is:

$$t(x) = 1 + \alpha^5 x = \alpha^0 + \alpha^5 x$$

## 3) Syndrome Polynomial Expansion Block

This block receives the syndrome polynomial s(x) and the erasure location polynomial t(x) from the preceding blocks. Its job is to multiply these two polynomials together to generate the modified syndrome polynomial, T(x). Continuing with the example, the received vectors were:

$$s(x) = \alpha^4 x^3 + \alpha^2 x^2 + \alpha^6 x + \alpha^5$$

$$t(x) = \alpha^0 + \alpha^5 x$$

T(x) is defined as:

$$T(x) = t(x)s(x)mod x^{2t}$$

$$T(x) = (\alpha^{0} + \alpha^{5}x)(\ \alpha^{4}x^{3} + \alpha^{2}x^{2} + \alpha^{6}x + \alpha^{5})\ mod\ x^{4}$$

$$T(x) = \alpha^5 + \alpha^4 x + \alpha^1 x^2 + \alpha^5 x^3$$

## 4) Erasure-Location Polynomial Generator Block

This block calculates the erasure location polynomial in parallel with the above syndrome expansion block. This block expands the erasure location polynomial. Given that the current example has only one erasure, the poly remains unchanged, but if for example both of the erroneous symbols in the example had been flagged, then t(x) would have been:

$$t(x) = (1 + \alpha^6 x)(1 + \alpha^5 x)$$

And in this case, this would need to be expanded by multiplying out the factors. In this case, the polynomial is unchanged and is forwarded as is,

$$D(x) = 1 + \alpha^5 x = \alpha^0 + \alpha^5 x$$

## 5) Errata Polynomials Generation Block

The job of this block is two create two key polynomials which will help to identify the location and magnitude of the errors in the codeword. The two polynomials are the errata-locator-polynomial,  $\Psi(x)$ , and the errata-magnitude-polynomial  $\Omega(x)$ . The inputs to this block are the modified syndrome polynomial, T(x), and the erasure-location-polynomial, D(x). There are two methods of computing these polynomials, the Berlekamp-Massey algorithm[28], or the Modified-Euclidean algorithm (MEA)[29]. In this work, the MEA algorithm will be used.

The MEA algorithm is a recursive algorithm which operates on 4 polynomials, R, Q, L, and U. They are initialized as follows:

- R is initialized to  $x^{2t}$

- L is initialized to 0

- Q is initialized with T(x)

- U is initialized with D(x)

The equations used to update the polynomial are:

$$R_{i}(x) = [\sigma_{i-1}b_{i-1}R_{i-1}(x) + \sigma^{\hat{}}_{i-1}a_{i-1}Q_{i-1}(x)] - x^{|l-1|}_{i}[\sigma_{i-1}a_{i-1}Q_{i-1}(x) + \sigma^{\hat{}}_{i-1}b_{i-1}R_{i-1}]$$

$$L_{i}(x) = [\sigma_{i-1}b_{i-1}L_{i-1}(x) + \sigma^{\hat{}}_{i-1}a_{i-1}U_{i-1}(x)] - x^{|l-1|}_{i}[\sigma_{i-1}a_{i-1}U_{i-1}(x) + \sigma^{\hat{}}_{i-1}b_{i-1}L_{i-1}]$$

$$Q_{i}(x) = \sigma_{i-1}Q_{i-1}(x) + \sigma^{\hat{}}_{i-1}R_{i-1}(x)$$

$$U_{i}(x) = \sigma_{i-1}U_{i-1}(x) + \sigma^{\hat{}}_{i-1}L_{i-1}(x)$$

where  $a_{i-1}$  and  $b_{i-1}$  are the leading coefficients of  $R_{i-1}(x)$  and  $Q_{i-1}(x)$ ,  $l_{i-1} = deg(R_{i-1}(x)) - deg(Q_{i-1}(x))$ , where deg(y) signifies the degree of y, and  $\sigma_{i-1} = 1$  if  $l_{i-1} \ge 0$ .  $\sigma`_{i-1}$  is the opposite of  $\sigma_{i-1}$ .

The number of iterations needed depends on the number of errors which were not flagged by the erasure generator. It can be seen that the more accurate the erasure generator, the better the performance of this block. The computation stops when the degree of  $R_i(x)$  is less than the degree of  $L_i(x)$ . When this occurs, the value of  $L_i(x)$  is output as the error-locator polynomial,  $\Psi(x)$ , and the value of  $R_i(x)$  is output as the error-magnitude polynomial,  $\Omega(x)$ . Continuing with the example, the initial values are:

$$R_0(x) = x^4$$

$$Q_0(x) = T(x) = \alpha^5 + \alpha^4 x + \alpha^1 x^2 + \alpha^5 x^3$$

$$L_0(x) = 0$$

$$U_0(x) = D(x) = \alpha^0 + \alpha^5 x$$

The end result of the MEA calculation results in:

$$\Psi(x) = \alpha^3 x^2 + \alpha^1 x + \alpha^1$$

$$\Omega(x) = \alpha^2 x + \alpha^6$$

## 6) Chien Search Block

The job of the Chien-Search block is to take the error-location  $(\Psi(x))$  and error magnitude  $(\Omega(x))$  polynomials, and evaluate them across all of the possible values in the  $GF(2^m)$ . In addition, the Chien-Search block creates and evaluates the derivative of  $\Psi(x)$ ,  $\Psi^*(x)$ , which is the odd terms of  $\Psi(x)$ .

When the result of an evaluation of  $\Psi(x)$  equals 0, it indicates that there is an error in the (n-i)th symbol in the codeword. These three sets of evaluations are passed on to the Forney Algorithm and Error-Correction Block. Continuing the example, the result of these calculations yields:

|            | $\Psi(x)$  | Ψ`(x)      | $\Omega(\mathbf{x})$ |

|------------|------------|------------|----------------------|

| $lpha^0$   | $\alpha^3$ | $\alpha^1$ | $lpha^0$             |

| $\alpha^1$ | $lpha^0$   | $\alpha^2$ | $\alpha^4$           |

| $\alpha^2$ | 0          | $\alpha^3$ | $\alpha^3$           |

| $\alpha^3$ | 0          | $lpha^4$   | $\alpha^1$           |

| $lpha^4$   | $\alpha^3$ | $\alpha^5$ | 0                    |

| $\alpha^5$ | $\alpha^1$ | $\alpha^6$ | $\alpha^2$           |

| $\alpha^6$ | $lpha^0$   | $lpha^0$   | $\alpha^5$           |

Table 2.2. Roots of Key Polynomials

These results indicate an error at location 7-2=5 and 7-3=4 in the received codeword, which is correct.

## 7) Forney Algorithm and Error-Correction Block

This block is responsible for evaluating the magnitude of each error indicated by the Chien-Search block and performing the correction to the original received codeword. It receives the evaluations of  $\Psi(x)$ ,  $\Psi^*(x)$ , and  $\Omega(x)$ , along with the original codeword from the FIFO. The magnitude of the error in location 1 is determined by the equation:

$$\hat{e}(\alpha^l) = \Omega(\alpha^l)/\Psi(\alpha^l)$$

A polynomial  $\hat{e}(x)$  is formed by combining the error locations (as powers of x) with the error magnitudes (as powers of  $\alpha$ ). The codeword is corrected by combining this polynomial with the original codeword polynomial, u(x), as follows:

$$\hat{c}(x) = \hat{e}(x) + u(x)$$

The result,  $\hat{c}(x)$ , is the corrected codeword. Following the example, errors are in location 5 and 4, corresponding to  $\alpha^2$  and  $\alpha^3$ . The error magnitudes are calculated as:

$$\hat{e}(\alpha^2) = \Omega(\alpha^2)/\Psi(\alpha^2) = \alpha^3/\alpha^3 = \alpha^0$$

$$\hat{e}(\alpha^3) = \Omega(\alpha^3)/\Psi^{\hat{}}(\alpha^3) = \alpha^1/\alpha^4 = \alpha^4$$

And thus the error vector  $\hat{e}(x)$  is:

$$\hat{e}(x) = \alpha^0 x^5 + \alpha^4 x^4$$

This vector is combined with u(x), the original received codeword, as follows:

$$\hat{c}(x) = \hat{e}(x) + r(x)$$

$$\hat{c}(x) = (\alpha^0 x^5 + \alpha^4 x^4) + (\alpha^3 x^6 + \alpha^1 x^5 + \alpha^2 x^4 + \alpha^4 x^3 + \alpha^0 x^2 + \alpha^4 x + \alpha^3)$$

$$\hat{c}(x) = \alpha^3 x^6 + \alpha^3 x^5 + \alpha^1 x^4 + \alpha^4 x^3 + \alpha^0 x^2 + \alpha^4 x + \alpha^3$$

$$\hat{c} = [011, 011, 010, 110, 001, 110, 011]$$

This creates the original codeword, as all errors have been corrected.

## 2.2) Energy Consumption in FPGAs

There are two distinct types of energy consumption in FPGAs, static and dynamic. Static energy is consumed by all parts of the FPGA, whether active or not, as

long as the device is on. Static energy is consumed at a roughly constant rate. The main source of static energy consumption is the SRAM used to store the configuration of the device. Static energy consumption can be viewed as the cost of having the FPGA device "on", and is roughly design independent, meaning that the opportunities for reducing static energy consumption available to the designer are limited.

The second type of energy consumption in FPGAs is dynamic energy consumption. This is caused by signal transitions in the circuitry as the application performs work. Dynamic energy consumption is the cost of the device performing calculations. The amount of energy consumed is governed by the capacitance on a particular signaling line, and each transition will generally dissipate the same amount of energy. There are two types of signal transitions, transitions necessary for calculations, and spurious transitions caused by path-delay differences in the logic circuits, which are commonly referred to as glitches.

In general, reducing the length (and thus the capacitance) of a signal line, or reducing the number of transitions across a line, whether required or spurious, will reduce dynamic energy consumption. This work focuses on high level techniques which reduce the total number of signal transitions.

# 2.3) Circuit Level Energy Reduction Methods

## 2.3.1) Pipelining

The impact of pipelining has previously been examined for a variety of different devices, and has been found to be effective at reducing energy consumption in digital

circuits[30]. Most recently, Wilton et al did an analysis of the effects of pipelining on energy consumption in FPGA circuits [8]. The conclusion of this study was that pipelining is an effective method of reducing dynamic energy consumption in FPGAs. Pipelining is especially applicable to FPGAs because a) the registers used for pipelining are embedded in the FPGA fabric in every logic element, so the cost of using them is minimal, and b) because the communication lines on FPGAs tend to be longer and have higher capacitance on average than those in a custom ASIC, signal transitions require a significant amount of energy. It is necessary to minimize spurious transitions on these lines, one of the beneficial effects of pipelining.

One effect of pipelining is to split the logic into discrete sections, separated by registers. By splitting the logic up, it is possible to selectively de-activate sections of logic by using clock gating, another method of energy reduction. The granularity of the pipelining determines the size of the logical register-to-register sections which can be clock gated, and thus the two methods have significant interaction.

The methodology used in this work to reduce energy via pipelining is as follows. Pipelining was performed by hand, to evaluate differing amounts of pipelining while maintaining identical logical functionality, differing only in latency. The initial designs are examined for areas which could potentially be pipelined. Examples of such areas include areas of large logic depths between registers. As we are attempting to minimize the amount of logic through which a glitch can propagate, it is desirable to separate functional units by inserting pipeline registers between them.

Although pipeline registers can reduce the propagation of glitches across logic and interconnect, and thus reduce energy consumption, the additional registers also

dissipate some amount of energy. Thus it is not always the case that additional pipelining will be effective in reducing energy, as a balance must be found between the energy saved from reduced glitching, and the energy consumed by additional registers. It was observed in preliminary work that there is a degree of pipelining which provides optimal energy per operation results. The goal is to find the optimal amount of pipelining to achieve minimal energy-per-operation performance.

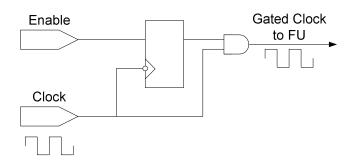

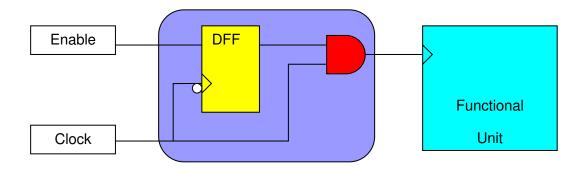

Figure 2.5. Clock Gating circuit

## 2.3.2) Clock Gating

Clock gating is a technique which has been shown to be effective for reducing power and energy consumption for all types of digital circuits [9] [10]. As illustrated in Figure 2.5, in its simplest form, clock gating is achieved by ANDing the clock signal to a particular element with an enable signal, so that when the enable is low, the combined signal is always forced low, effectively halting any clocked operations in any logic controlled by that clock signal. This is done to reduce unnecessary transitions in the logic, thus reducing dynamic energy consumption. Typically, we gate computational elements

when the results of their computation is unneeded, meaning the results have no impact on a current or future output signal. Clock gating is particularly applicable to FPGA circuits because the ability to enable and disable the clock is typically built into the logic elements in the FPGA, so the cost of using them is minimal. Preventing a transition on an interconnect line is particularly beneficial for FPGAs since interconnect capacitance is quite high compared to ASICs.

Despite these advantages, clock gating has significant tradeoffs. While energy may be saved by preventing unnecessary computation, additional energy will be consumed by the gating logic, and the designer must make sure that the energy saved exceeds the additional energy of the gating logic. In addition, the generation of clock gating control signals can sometimes introduce additional levels of logic, reducing the maximum operational frequency of the design.

Our methodology for applying clock gating is as follows. Given a design which has previously been pipelined, we have the option of gating a register, effectively cutting off any computation driven by the output of that register. We begin by examining the application for areas whose computation will not always be needed. For example, in a pipelined ALU, there are separate functional units for every operation, AND, OR, ADD/SUB, etc. Each particular unit is only needed when a particular operation is needed. Thus, it makes sense to gate portions of the functional unit based on the value of the required operation. In addition, given a pipelined architecture, it is often possible to know which units will be needed a cycle or more ahead of time. If this is the case, it is possible to perform cycle-ahead gating.

Once areas have been identified for possible clock gating, the designer must weigh the energy consumption of the logic needed to generate the enable signal against the energy which can be saved when the functional logic is gated. This depends not only on the amount of logic which is gated, but the percentage of the time that the logic will actually be used, which often depends on the incoming data. Often, it is a matter of running simulations based on expected data to determine the viability of reducing energy consumption via gating a particular section of logic.

To gate a clock, the designer needs to provide a control signal which allows logic to operate only when it is needed. In the ALU example, a simple solution is to use a combination of operand signals to create a gating signal. This control signal is then connected with the clock to an AND gate, so that when the enable signal is low, the clock is forced to remain low.

One final note is that it can be seen from the above discussion that we can only gate contiguous sections of logic, separated by registers. The granularity of the possible gating thus depends on the degree of pipelining applied to the circuit.

The end goal of clock gating the Reed-Solomon decoder design is to ensure that the various functional units only receive a clock when they are currently processing data. Because each of the units in the decoder takes a different amount of time to perform its operations, there is significant downtime among some of the functional units in the design.

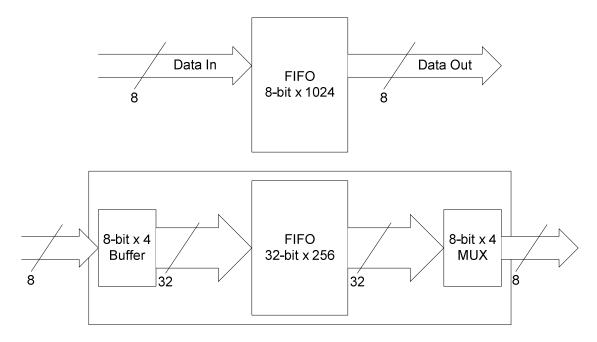

## 2.3.3. Memory Access Reduction Techniques

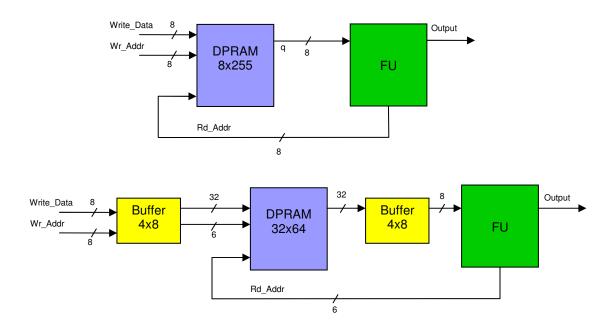

Clock gating of embedded memory units is of particular interest in FPGAs, due to their high energy consumption rates when compared to general logic circuitry. Rather than clock gating an entire memory, it is possible to re-format a memory unit and insert small buffers before and/or after an embedded memory to allow it to be gated for larger periods of time. This is accomplished by reconfiguring the memory to have a bus size which is a multiple of the original width, reducing the overall number of elements, keeping the same overall size constant. The buffers then combine data from two or more contiguous writes into one data point, and similarly read a large data point and then provide each unit of the data to the logic separately, one after the other. Figure 2.6 and 2.7 below illustrate this concept.

Figure 2.6. Memory Buffering

| 8-bit Write | 8-bit Write | 8-bit Write | 8-bit Write  | 8-bit Write | 8-bit Write | 8-bit Write | 8-bit Write  |

|-------------|-------------|-------------|--------------|-------------|-------------|-------------|--------------|

| ldle        |             |             | 32-bit Write | Idle        |             |             | 32-bit Write |

Figure 2.7. Activity of Memory, original vs. buffered

Figure 2.6 illustrates the structural differences between a typical memory setup (above), and the buffered setup (below). The buffered setup collects four 8-bit data points before performing each 32-bit write to the embedded memory block. On the read side, one 32-bit data point is read every four clock cycles, and 8-bits are presented to the output every cycle. Figure 2.7 illustrates the activity of the embedded memory under the typical and buffered schemes. From the activity diagram, it is evident that the activity of the memory can be reduced by 75% by buffering.

This method allows the memory to be deactivated for half or more of the time it would have previously been active, reducing energy consumption significantly. While some extra energy will be consumed by the buffers, it is typically much less than the energy saved by deactivating the memory. A caveat of this method is that it is only possible when the data will be written and read in order, otherwise this method is not applicable.

## 2.4. Dynamic Reconfiguration

One of the other methods used in this work is the concept of dynamic reconfiguration. Dynamic reconfiguration refers to the technique of changing the

functionality of a component during operation, to achieve a specific goal such as increased performance, reduced power consumption, increased speed, etc. Previous works have shown dynamic reconfiguration of FPGA based applications to be effective for many goals, including reducing the size of the necessary hardware component [12], for the support of concurrent applications[32], and directly related to this work, to reduce power consumption and increase performance [15]. This particular work will examine dynamic reconfiguration for energy efficiency, essentially attempting to minimize the amount of energy needed to decode a certain amount of data, and reconfiguring as channel conditions allow in order to swap in a more efficient decoder. The methodology of this process will be examined in Chapter 4.

#### CHAPTER 3

#### RELATED WORK

#### 3.1. Previous RS works

This section will contain an overview of previous works in the area of Reed-Solomon decoders. As mentioned in the introduction, this system is designed to provide Reed-Solomon decoder functionality for a system which is already FPGA based, as the performance and energy consumption characteristics of an FPGA based RS decoder are unlikely to better an ASIC implementation.

## 3.1.1. A Low-Power Reed-Solomon Decoder for STM-16 Optical Communications

This paper [21] describes a low-power ASIC implementation of a Reed-Solomon (255,239) decoder, designed for submarine communications. It is included here to illustrate the current performance levels of ASIC implementations of the Reed-Solomon algorithm. The design implements a novel syndrome calculation unit, along with a modified Berlekamp-Massey algorithm as opposed to an implementation of the MEA or EA algorithms to solve the key equations. The chip was implemented using .25um CMOS standard cells. The resulting performance characteristics are a sustained 2.5Gbps throughput with a CER of 10<sup>-4</sup>, and the entire chip consumes 68.5mW of power. Calculating the energy-per-codeword value from these characteristics, it is clear that each bit requires approximately 2.74x10<sup>-11</sup> J to process. Comparing this to the previous work, which required approximately 1.25x10<sup>-9</sup> J to process a bit, counting dynamic power only, it is unlikely that any FPGA implementation of an RS decoder will be able to beat the

ASIC in terms of energy consumption. This is why this work is aimed at systems already containing an FPGA for processing, in which case the RS decoder can be added to the existing FPGA code instead of requiring an external RS ASIC.

# 3.1.2. Design of a Reed-Solomon Decoder using Partial Reconfiguration of XILINX FPGAs – A Case Study

This paper [12] uses a Reed-Solomon coder and decoder to test a design methodology aimed at allowing for partial run-time reconfiguration of applications. The design uses both static modules, and so called pRTR modules, which are the partial run-time reconfigurable parts of the design. The design works by maintaining the same overall structure by loading pRTR units as needed into the same physical location. It makes use of a static CLB interface macro to handle communications between modules. The seven pRTR modules encompassing the RS encoder and decoder are: RS coder, RS decoder, syndrome calculation, error locations, error locator polynomial, error magnitudes, and error corrections. The design allows for the system to be implemented on a small FPGA by swapping in and out the modules as they are needed.

Unlike the above approach, the approach used in this work makes use of full dynamic reconfiguration. In addition, the reconfiguration is used to adapt to changing channel conditions, not allow for implementation of the design on area-limited devices.

3.1.3. Architecture for Decoding Adaptive Reed-Solomon Codes with Variable Block Length

This work [13] describes the implementation of an adaptive RS decoding system on an Altera APEX20KE FPGA. The system adapts to allow for varying block lengths between 13 and 255, while maintaining error correction capabilities of up to 10 erroneous bytes in a codeword. The goal of this work is to maintain the needed CER by varying the amount of redundancy in the symbol. With this design, the value of t can be varied on a codeword to codeword basis. The design makes use of a multiplexed MEA unit, which allows for pipelined operation of the design. The resultant data rate achieved is 240Mbps, with a resource utilization of approximately 17,000 LUTs.

The main difference between this and the work described in this document is that the system in this work does not vary the block length, it varies the value of K. This allows for less communication between the encoder and decoder, which is desirable in a real-world system. As the goal of this work was to reduce energy consumption over speed, the multiplexed MEA structure is not desirable. Lastly, our system is able to correct more errors given that it implements erasures. The use of erasures allows for a reduction on the load of the MEA unit, and thus a faster operation of this part of the algorithm.

3.1.4. A Reed-Solomon Decoder with Efficient Recursive Cell Architecture for DVD Applications

This paper presents an errors-only RS(208,192) decoder implemented on an Altera FLEX10KE200 FPGA [14]. The goal of this work was to examine and design an

efficient MEA architecture which would reduce the time to compute MEA by 32% compared to standard architectures. The design makes use of a reduced number of MEA cells, which are multiplexed and used recursively. The design makes use of the number of MEA cells needed so that the computation is not limited by the MEA block. This means that the computation must be performed in n clock cycles, as this is the number of clock cycles between codewords. For the RS(208,192) decoder, this needs only one MEA cell. However, if the architecture was used on larger decoders, such as RS(255,223), it would require 4 MEA cells. The architecture achieves a decoding speed of 20Mbps.

In the proposed work, again, the decoder can correct more errors by using an errors-and-erasures approach. This allows for a reduction in the necessary processing using the MEA unit, and thus one MEA unit can be used recursively, which also reduces overall energy consumption compared to the above work.

## 3.2. Previous FPGA Energy Reduction Works

This section will highlight previous works involving reduction of FPGA energy consumption.

3.2.1. The Impact of Pipelining on Energy per Operation in Field-Programmable Gate Arrays

This work by Wilton [8] examines the impact of pipelining on energy consumption for FPGA designs. The study used 4 benchmarks, 64-bit Integer Array Multiplication, Triple DES encryption, 8-tap FIR filter, and a CORDIC circuit. These designs were implemented with varying degrees of pipelining ranging from one or 2

levels to the maximum possible amount of pipelining, a register after every LUT. The result of the work demonstrates that pipelining can reduce the overall energy-per-operation values across all of the benchmarks, by as much as 75%. However, with some benchmarks, there is a reduction in benefits as more and more pipeline stages are introduced, suggesting that there is a particular amount of pipelining at which the best energy performance can be achieved.

An approach similar to the one used above, although less exhaustive, was used in this work to examine exactly how much pipelining is beneficial in the design.

## 3.2.2. Energy-Efficient Signal Processing Using FPGAs

In this work by Choi et al, [10], algorithmic level energy optimizations were examined for their impacts of energy dissipation in several FPGA applications. The applications studied were the Fast Fourier Transform (FFT) and Matrix Multiplication. The methods used to reduce energy were Architecture Selection, Module Disabling, Algorithm Selection, Pipelining, and Parallel Processing. Module disabling is essentially implemented by using clock gating to restrict the clock from propagating to sections of the logic when no result is needed. One of the main uses of this technique in this work is to clock gate the memories when they are not in use. The authors point out through simulations that an embedded FPGA memory block will dissipate approximately 10% of the energy when it is disabled than it would if enabled.

This technique was adopted with great success in this work given the large number of embedded memory units required by the design. In addition, clock gating, as mentioned in Chapter 2, was expanded to include any functional unit which can be switched off for any amount of time.

### 3.3. An Adaptive Reed-Solomon Errors-and-Erasures Decoder

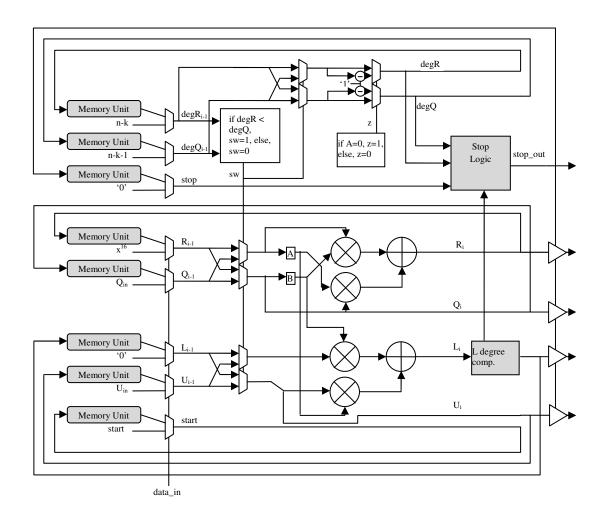

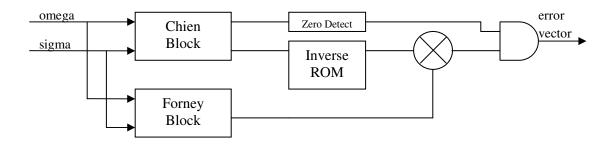

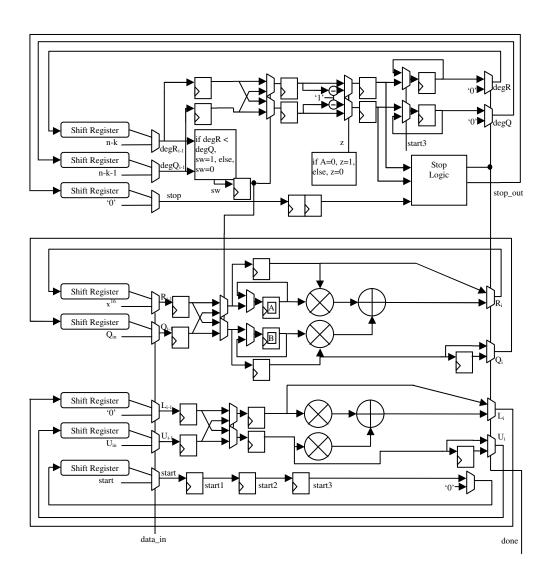

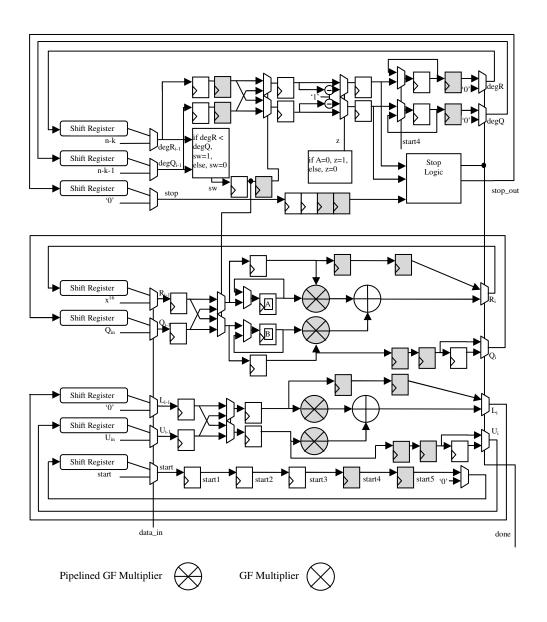

This section will provide a detailed description of the Reed-Solomon errors-anderasures decoder system developed by Lilian Atieno as part of her masters thesis [15]. The resultant work was presented at the Proceedings of the ACM/SIGDA International Symposium on Field Programmable Gate Arrays, Monterey, CA, February 2006 [7], and can be referred to for more in depth analysis of her work. The work described in this document uses this previous work as a baseline to improve upon.