# A Novel Approach to Pci Simulation Using ScriptSim

| Item Type     | thesis                                    |  |

|---------------|-------------------------------------------|--|

| Authors       | Andryc, Kevin R                           |  |

| DOI           | 10.7275/497979                            |  |

| Download date | 2025-05-01 10:11:14                       |  |

| Link to Item  | https://hdl.handle.net/20.500.14394/44740 |  |

# A NOVEL APPROACH TO PCI SIMULATION USING SCRIPTSIM

A Thesis Presented

by

KEVIN R. ANDRYC

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE IN ELECTRICAL AND COMPUTER ENGINEERING

May 2008

Electrical and Computer Engineering

© Copyright by Kevin R. Andryc 2008

All Rights Reserved

# A NOVEL APPROACH TO PCI SIMULATION USING SCRIPTSIM

A Thesis Presented

by

# KEVIN R. ANDRYC

Approved as to style and content by:

Russell G. Tessier, Chair

Patrick A. Kelly, Member

Eric Polizzi, Member

C. V. Hollot, Department Head Electrical & Computer Engineering

#### ABSTRACT

# A NOVEL APPROACH TO PCI SIMULATION USING SCRIPTSIM MAY 2008 KEVIN ANDRYC, B.S., UNIVERISTY OF MASSACHUSETTS

# M.S.E.C.E., UNIVERISTY OF MASSACHUSETTS

# Directed by: Professor Russell G. Tessier

In recent years, the Peripheral Component Interconnect (PCI) has become one of the most widely used bus architectures in modern computers. Simulation of the PCI bus, however, has been limited in both research and development. Current commercial PCI simulation software is designed towards compliance and verification testing rather than accurately mimicking PCI bus systems. In addition, most PCI simulation software is inflexible and offers no graphical user interface, instead relying on text files for configuration.

This paper presents a novel approach to PCI simulation using ScriptSim, an opensource PCI simulation tool that supports all the features offered by the PCI Local Specification Version 2.2. In addition to extending ScriptSim to include PCI-X functionality and a web-based graphical interface, we introduce techniques that allow us to accurately simulate real-world systems.

# TABLE OF CONTENTS

| ABSTRACT                                           |                                                                                                                                                                                                                | iv                               |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| LIST OF TABLES                                     |                                                                                                                                                                                                                | ix                               |

| LIST OF FIGURES .                                  |                                                                                                                                                                                                                | xi                               |

| CHAPTER                                            |                                                                                                                                                                                                                |                                  |

| 1. INTRODUCTION                                    | 1                                                                                                                                                                                                              | 1                                |

| 1.2 Contribut                                      | on<br>tions                                                                                                                                                                                                    | 5                                |

| 2. CURRENT BUS S                                   | SYSTEMS                                                                                                                                                                                                        | 7                                |

| 2.1 Bus Syste                                      | ems                                                                                                                                                                                                            | 8                                |

| 2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7 | Industry Standard Architecture Bus<br>VersaModule Eurocard Bus<br>FutureBus / FutureBus+<br>InfiniBand Architecture.<br>Universal Serial Bus<br>IEEE-1394 Serial Bus / FireWire.<br>Accelerated Graphics Port. | 10<br>11<br>12<br>13<br>15<br>16 |

|                                                    | Peripheral Component Interface Express                                                                                                                                                                         |                                  |

|                                                    | I-Bus Systems in Real-Time Environments                                                                                                                                                                        |                                  |

| 3.1.2<br>3.1.3                                     | Simplified PCI-Bus Model<br>Model for Identical Devices<br>Model for Arbitrary Devices<br>Concluding Remarks                                                                                                   | 23<br>26                         |

| 3.2 Simulatio                                      | on Software                                                                                                                                                                                                    | 31                               |

|                                                    | JSIM: A Java-Based Simulation and Animation<br>Environment<br>Building a Web-Based Federated Simulation System with                                                                                            | 31                               |

|                                                    | Jini and XML                                                                                                                                                                                                   | . 32                             |

| 3.2.3 Design and Implementation of PCI Bus Based Systems | 34 |

|----------------------------------------------------------|----|

| 4. PERIPHERAL COMPONENT INTERFACE                        | 44 |

| 4.1 PCI Bus Characteristics                              | 44 |

| 4.2 Used Terms and Conventions                           |    |

|                                                          |    |

| 4.2.1 Used Terms                                         | 46 |

| 4.2.2 Document Conventions                               | 48 |

| 4.3 PCI Bus Signal Descriptions                          | 49 |

| 4.3.1 Signal Types                                       | 49 |

| 4.3.2 Signal Groups                                      |    |

|                                                          |    |

| 4.4 PCI Bus Commands                                     | 59 |

| 4.5 PCI Address Structure                                | 62 |

| 4.5.1 Memory Address Space                               | 63 |

| 4.5.1 Wennory Address Space                              |    |

| 4.5.3 Configuration Address Space                        |    |

|                                                          |    |

| 4.6 PCI Configuration                                    | 66 |

| 4.6.1 Configuration Header                               | 66 |

| 4.7 PCI Bus Transactions                                 | 77 |

| 4.7.1 Read Transaction                                   | 78 |

| 4.7.2 Write Transaction                                  |    |

|                                                          |    |

| 4.8 PCI Bus Arbitration                                  | 81 |

| 5. PERIPHERAL COMPONENT INTERCONNECT EXTENDED            | 83 |

| 5.1 PCI-X Bus Commands                                   | 84 |

| 5.2 PCI-X Bus Transactions                               |    |

|                                                          |    |

| 5.2.1 Write Transaction                                  | 85 |

| 5.3 Burst and DWORD Transactions                         | 86 |

| 5.4 Allowable Disconnect Boundaries                      |    |

| 5.5 Attributes and the Attribute Phase                   | 87 |

| 5.6 Split Transactions                                   | 89 |

| 5 C 1 Cull Deserves                                      | 00 |

| 5.6.1 Split Response                                     | 90 |

| 5.6.2 Split Completion                             | 90  |

|----------------------------------------------------|-----|

| 5.7 Configuration and Initialization               | 93  |

| 5.7.1 Configuration Transaction Timing             | 95  |

| 5.7.2 Configuration Address                        |     |

| 5.7.3 Configuration Attributes                     |     |

| 5.7.4 Configuration Header                         |     |

| 5.7.5 PCI-X Capabilities List Item                 | 98  |

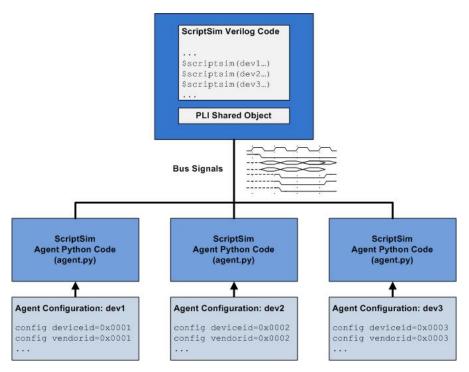

| 6. SCRIPTSIM                                       | 103 |

| 6.1 PCI Functional Bus Model                       | 104 |

| 6.2 PCI Bus Model Architecture                     |     |

| 6.3 PCI Bus Simulation                             |     |

| 6.3.1 Verilog Instantiation                        | 106 |

| 6.3.2 Configuration and Activity Generation        |     |

| 0.5.2 Comiguration and relivity Ceneration         |     |

| 7. IMPLEMENTATION OF THE PCI SIMULATOR             | 113 |

| 7.1 Methodology                                    | 113 |

| 7.1.1 Modeling Behavior                            | 114 |

| 7.2 Architecture of the PCI Simulator              | 118 |

| 7.3 Implementation of the Graphical User Interface | 119 |

| 7.3.1 GUI System Design                            | 119 |

| 7.3.2 Web Application Architecture                 |     |

| 7.3.3 Design Patterns                              |     |

| 7.3.4 User Interface Design                        |     |

| 7.3.5 Site Map                                     |     |

| 7.3.6 Functional Design                            |     |

| 7.4 Modification and Implementation of ScriptSim   | 140 |

| 7.4.1 Device Latency and Synchronization           | 141 |

| 7.4.2 Implementing Device Behavior                 |     |

| 8. EXPERIMENTAL RESULTS                            | 147 |

| 8.1 Simulation 1: Single PCI Master                | 149 |

| 8.2 Simulation 2: Two PCI Masters                  |     |

| 8.3 Simulation 3: Single PCI-X Master              |     |

| 9. SUMMARY      |  |

|-----------------|--|

| 9.1 Conclusion  |  |

| 9.2 Future Use  |  |

| 9.3 Future Work |  |

| REFERENCES      |  |

| Table                                                                             | Page |

|-----------------------------------------------------------------------------------|------|

| 2.1: Comparison of various common bus systems                                     | 10   |

| 3.1: Simulation target parameters                                                 | 40   |

| 3.2: Simulation master parameters                                                 | 41   |

| 4.1: PCI bus command types                                                        | 53   |

| 4.2: PCI burst ordering modes                                                     | 63   |

| 4.3: Valid byte combinations of BE#[3:0] and AD[1::0] for I/O read/write commands | 64   |

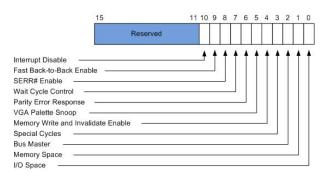

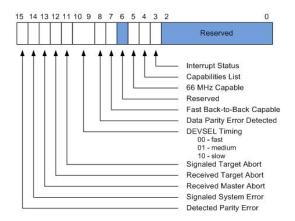

| 4.4: Configuration command register bits                                          | 70   |

| 4.5: Configuration status register bits                                           | 72   |

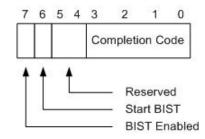

| 4.6: Configuration built-in self test register bits                               | 73   |

| 5.1: PCI versus PCI-X bus command encodings                                       |      |

| 5.2: Description of fields associated with DWORD transactions                     |      |

| 5.3: Split completion address field definitions                                   | 91   |

| 5.4: Completer attribute field definitions                                        |      |

| 5.5: Split completion message fields                                              |      |

| 5.6: PCI-X mapping of the device number to the upper AD lines                     | 96   |

| 5.7: PCI-X Command Register description                                           |      |

| 5.8: PCI-X Command Register description                                           |      |

| 6.1: ScriptSim agent parameters                                                   | 106  |

| 6.2: ScriptSim arbiter parameters                                                 |      |

| 6.3: ScriptSim monitor parameters                                                 |      |

| 6.4: Master keyword descriptions                                                  | 111  |

# LIST OF TABLES

| 6.5: Target keyword descriptions                        | . 112 |

|---------------------------------------------------------|-------|

| 6.6: Verilog task call parameters                       | . 112 |

| 7.1: Extended master keyword descriptions               | . 146 |

| 7.2: Extended target keyword descriptions               | . 146 |

| 8.1: Summary list of experiments                        | . 148 |

| 8.2: Master performance specifications for simulation 1 | . 150 |

| 8.3: Target performance specifications for simulation 1 | . 150 |

| 8.4: Master performance specifications for simulation 2 | . 152 |

| 8.5: Target performance specifications for simulation 2 | . 152 |

| 8.6: Master performance specifications for simulation 3 | . 155 |

| 8.7: Target performance specifications for simulation 3 | . 156 |

# LIST OF FIGURES

| Figure Page                                                                      |

|----------------------------------------------------------------------------------|

| 1.1: Relation between burst size and both latency and maximum bandwidth          |

| 1.2: Modern PC architecture                                                      |

| 2.1: Modern computer system which uses both synchronous and asynchronous buses 8 |

| 2.2: USB device hierarchy                                                        |

| 2.3: IEEE-1394 bus cycle with isochronous and asynchronous data                  |

| 2.4: Two PCIe devices connected by a link consisting of 4 lanes                  |

| 3.1: Two identical devices with $D = (4, 3, 8)$                                  |

| 3.2: Two identical devices with $D = (4, 3, 6)$                                  |

| 3.3: Two sample devices with $D_1 = (4, 3, 6)$ and $D_2 = (3, 4, 7)$             |

| 3.4: Two devices, multiple transactions, with delay                              |

| 3.5: Two devices, multiple transactions, without delay                           |

| 3.6: Hypothetical system used for PCI simulation                                 |

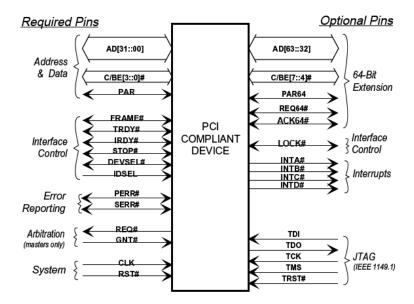

| 4.1: PCI bus signals as defined by the PCI standard                              |

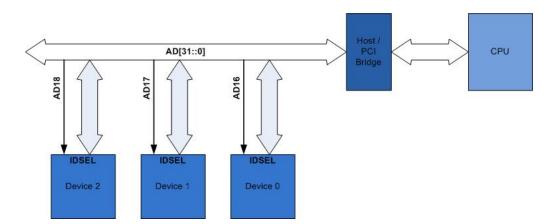

| 4.2: IDSEL during a configuration command                                        |

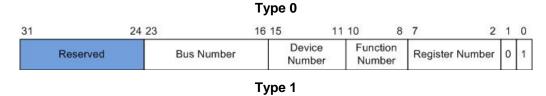

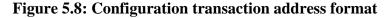

| 4.3: Address phase interpretation during a configuration transaction             |

| 4.4: Type 0 configuration header67                                               |

| 4.5: Configuration command register layout                                       |

| 4.6: Configuration status register layout71                                      |

| 4.7: Configuration built-in self test register layout73                          |

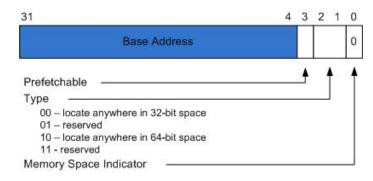

| 4.8: Base Address Register for Memory Space                                      |

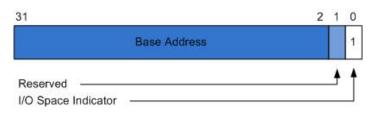

| 4.9: Base Address Register for I/O Space                                         |

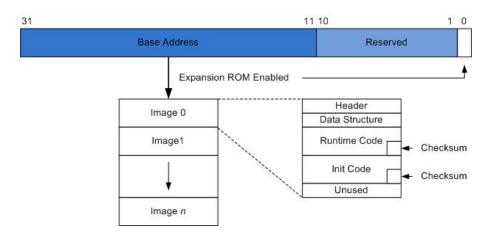

| 4.10: Expansion ROM Base Address Register                            | 7 |

|----------------------------------------------------------------------|---|

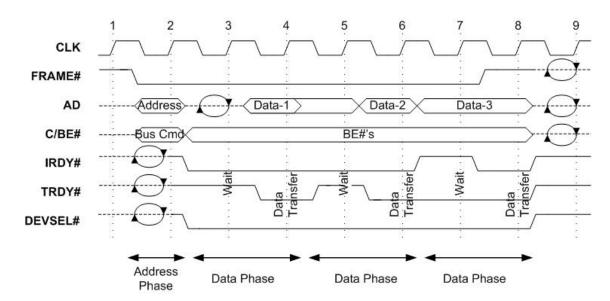

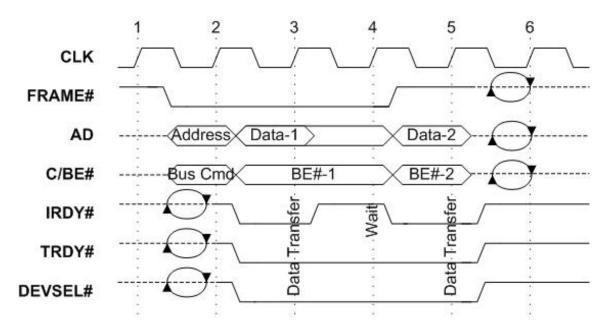

| 4.11: Timing diagram for a typical PCI read transaction              | 9 |

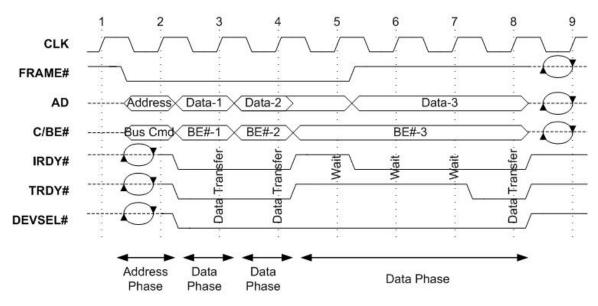

| 4.12: Timing diagram for a typical PCI write transaction             | 1 |

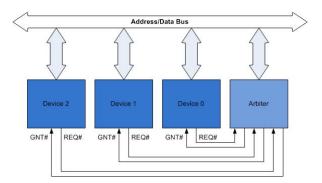

| 4.13: PCI arbitration                                                | 1 |

| 4.14: Priority scheme algorithm for fair arbitration                 | 2 |

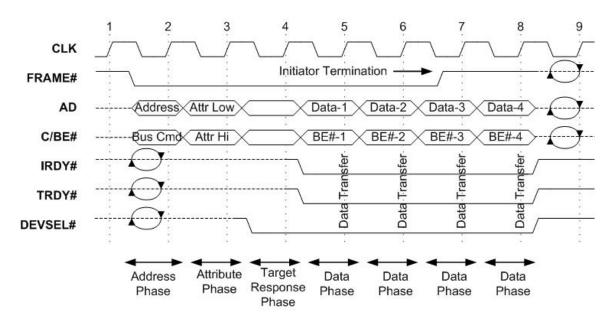

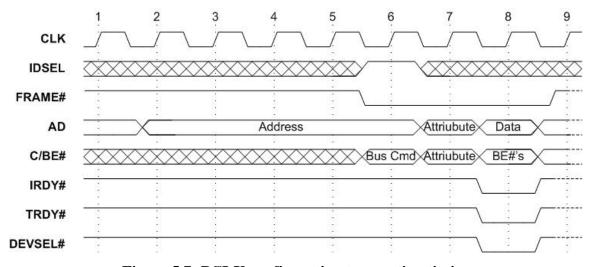

| 5.1: Timing diagram for a typical PCI-X write transaction            | 5 |

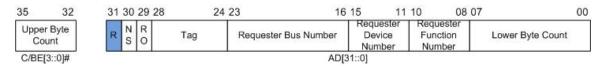

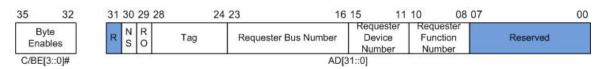

| 5.2: Burst transaction attributes                                    | 3 |

| 5.3: DWORD transaction attributes                                    | 3 |

| 5.4: Split completion address                                        | 1 |

| 5.5: Split completion completer attributes                           | 2 |

| 5.6: Split completion message                                        | 3 |

| 5.7: PCI-X configuration transaction timing                          | 4 |

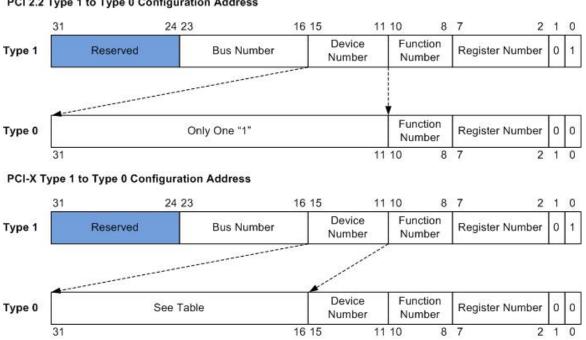

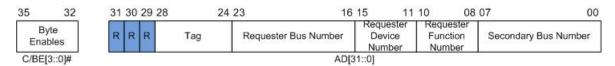

| 5.8: Configuration transaction address format                        | 5 |

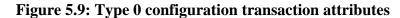

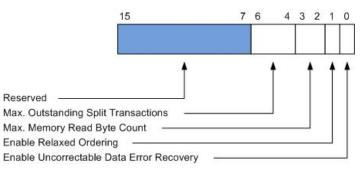

| 5.9: Type 0 configuration transaction attributes                     | 5 |

| 5.10: PCI-X Capabilities List format                                 | 9 |

| 5.11: PCI-X Command Register format                                  | 9 |

| 5.12: PCI-X Status Register format                                   | 1 |

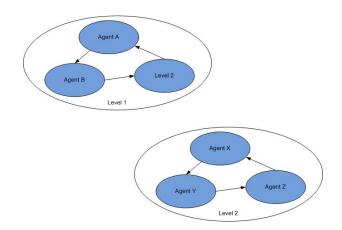

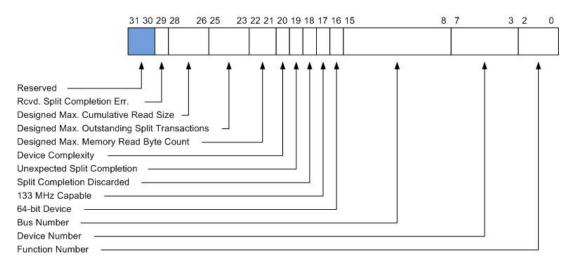

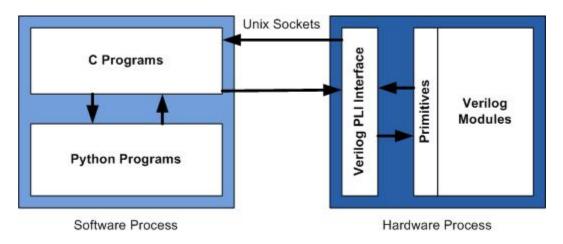

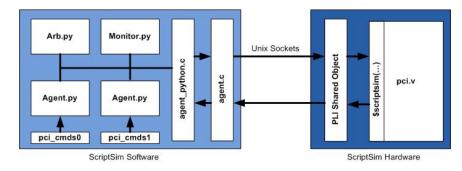

| 6.1: ScriptSim architecture                                          | 3 |

| 6.2: ScriptSim PCI bus model architecture                            | 5 |

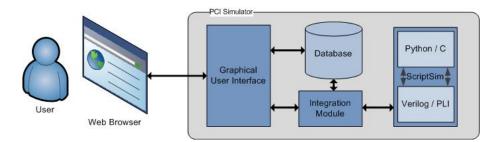

| 7.1: PCI Simulator system architecture                               | 9 |

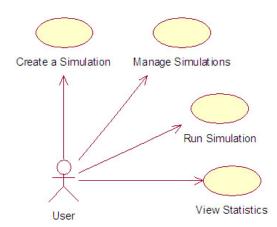

| 7.2: Use case diagram of the PCI simulation application              | ) |

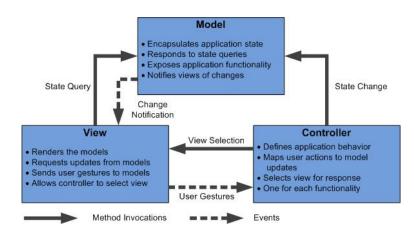

| 7.3: Model-View-Controller architecture                              | 1 |

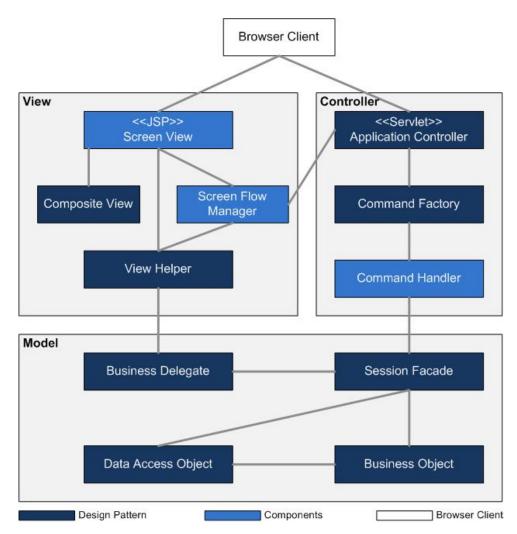

| 7.4: MVC architecture decomposed into design patterns and components | 3 |

| 7.5: PCI Simulator design interface                                | 124 |

|--------------------------------------------------------------------|-----|

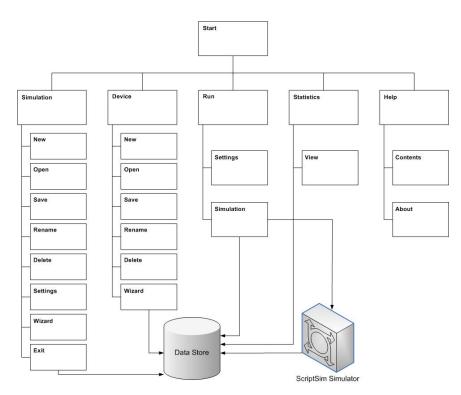

| 7.6: PCI Simulator site map                                        | 125 |

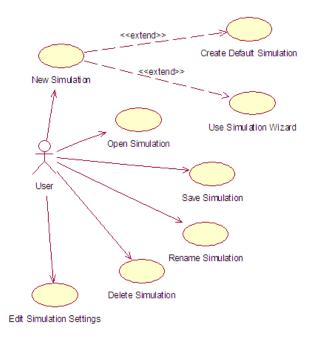

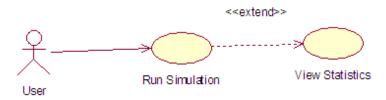

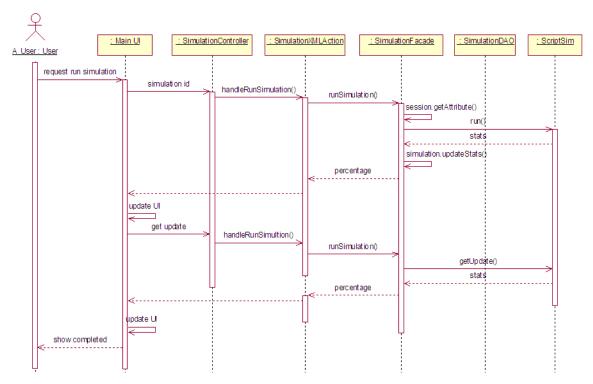

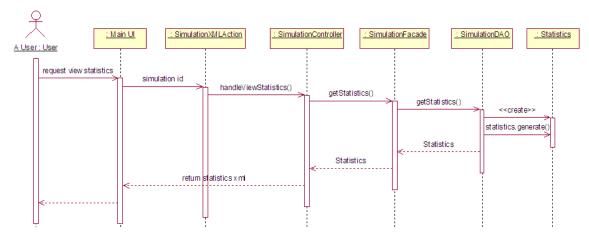

| 7.7: Simulation use case                                           | 126 |

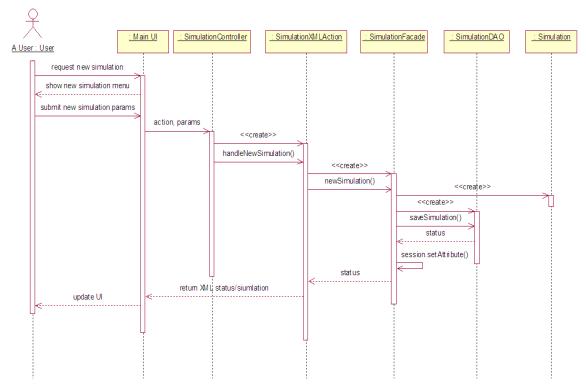

| 7.8: New simulation sequence diagram                               | 127 |

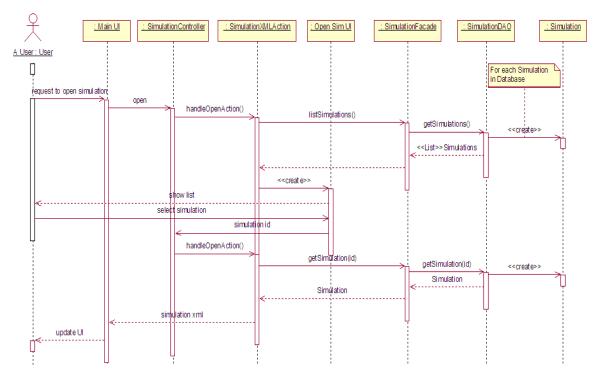

| 7.9: Open simulation sequence diagram                              | 128 |

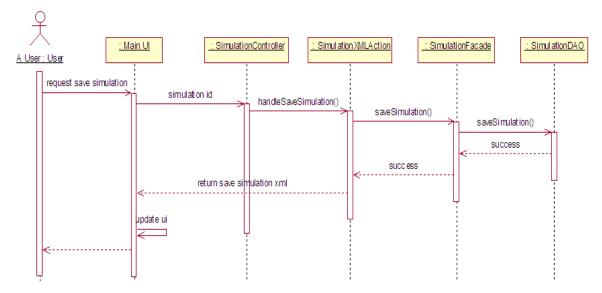

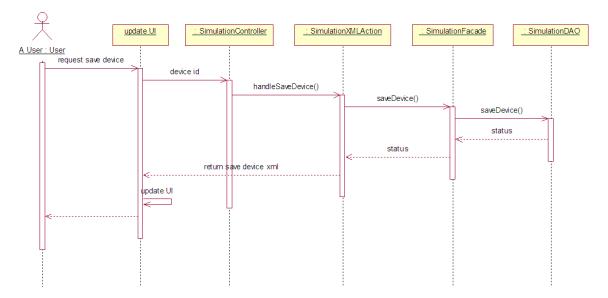

| 7.10: Save simulation sequence diagram                             | 129 |

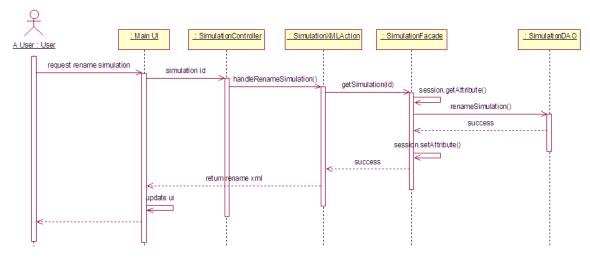

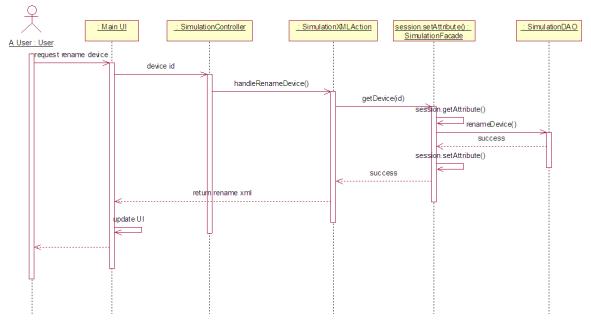

| 7.11: Rename simulation sequence diagram                           | 130 |

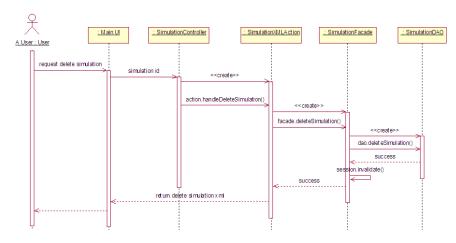

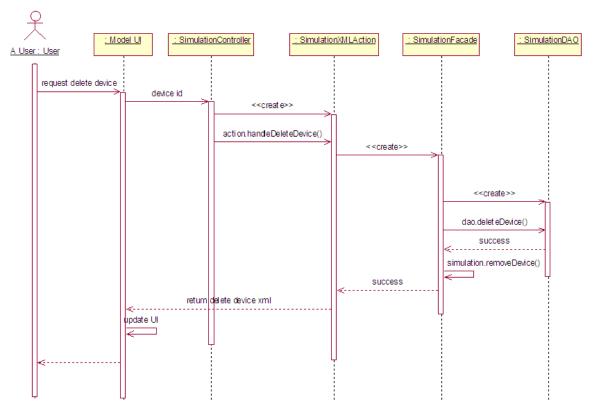

| 7.12: Delete simulation sequence diagram                           | 131 |

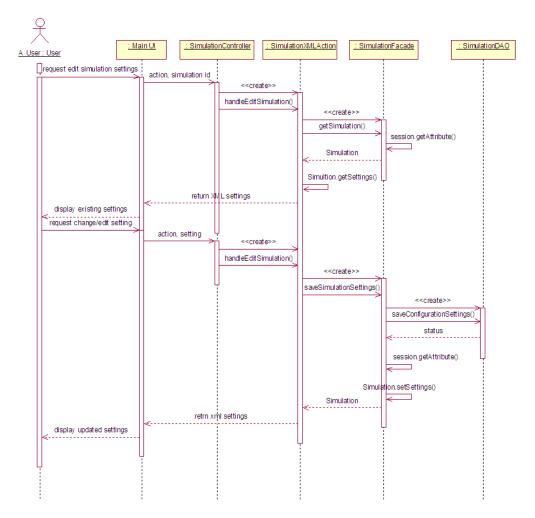

| 7.13: Simulation settings sequence diagram                         | 132 |

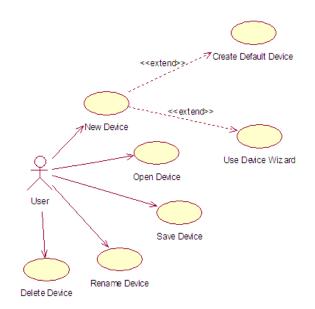

| 7.14: Device use case                                              | 133 |

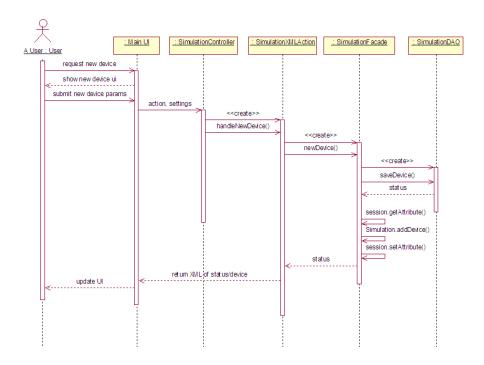

| 7.15: New device sequence diagram                                  | 134 |

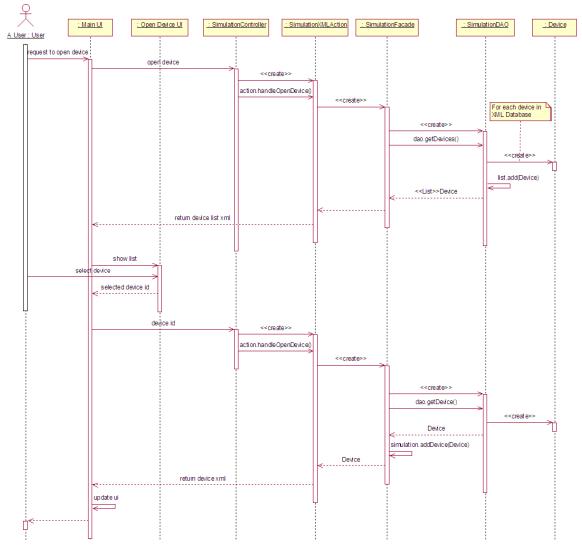

| 7.16: Open device sequence diagram                                 | 135 |

| 7.17: Save device sequence diagram                                 | 136 |

| 7.18: Rename device sequence diagram                               | 137 |

| 7.19: Delete device sequence diagram                               | 138 |

| 7.20: Run simulation use case                                      | 138 |

| 7.21: Run simulation sequence diagram                              | 139 |

| 7.22: View statistics sequence diagram                             | 140 |

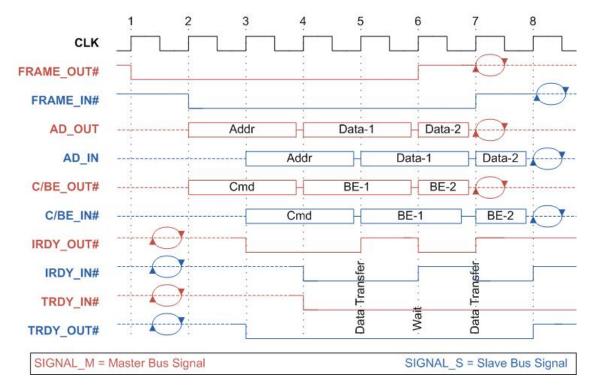

| 7.23: Typical PCI write transaction                                | 142 |

| 7.24: High-level view of bus signal distribution in ScriptSim      | 143 |

| 7.25: PCI write transaction in ScriptSim                           | 144 |

| 8.1: Experimental system setup                                     | 148 |

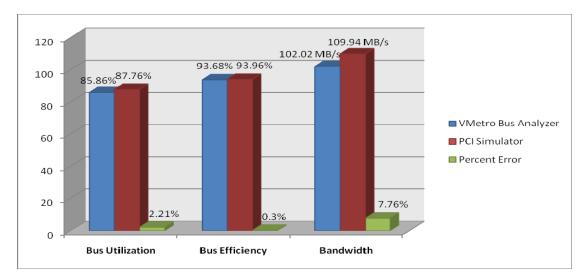

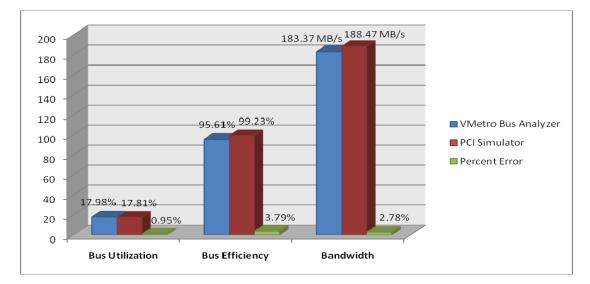

| 8.2: VMetro analyzer versus PCI simulator results for simulation 1 | 151 |

| 8.3: | VMetro | analyzer | versus PC | I simulator | results t | for si | mulation | 2 | <br>153 |

|------|--------|----------|-----------|-------------|-----------|--------|----------|---|---------|

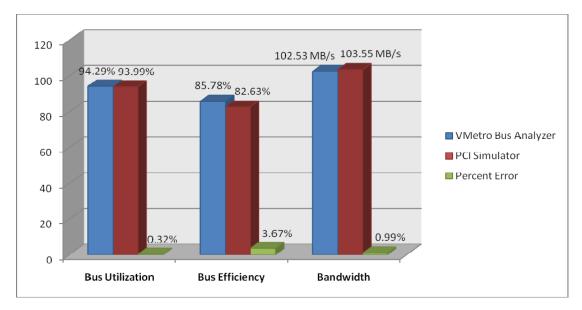

| 8.4: | VMetro | analyzer | versus PC | I simulator | results t | for si | mulation | 3 | <br>154 |

#### **CHAPTER 1**

#### **INTRODUCTION**

Traditionally, PCI simulation software, like Synopsys' DesignWare PCI IP [18], is specifically designed for verification and compliance of the PCI/PCI-X standard. While these simulators provide accurate models to test complex user-developed hardware, they do not provide the means to accurately measure performance based on real-life systems. While some simulators take into account external factors that may affect performance, such as memory latency, they are either statically defined or targeted towards a specific architecture. In addition, most simulators allow for configuration using text files or by manually editing the source program which requires timely recompilation for each change. Furthermore, simulating bus activity requires the user to individually add commands to each device. While this allows the user greater detail and control over bus activity, it is also timely and can become unwieldy. The goal of this thesis is to propose a novel approach to PCI simulation by taking into account external system factors in addition to providing an easy to use interface.

# 1.1 Motivation

The main characteristic of simulators is the ability to model real-life situations. Having accurate models will help designers make informed decisions and help reduce costly mistakes. When designing hardware to be used on the PCI bus, knowing what type of performance to expect is essential. The design of a PCI simulator can be a complicated proposition. While ensuring the simulator meets the specifications set by the PCI Special Interest Group (PCISIG), it is important to model the effects of devices and system components in obtaining accurate performance measures. However, the design of the user

interface is just as important. It should provide all the functionality necessary to easily perform simulations while also being flexible enough to allow the designer to customize it to adjust various parameters.

Bus performance is usually measured by its theoretical *peak bandwidth*. While the peak bandwidth is easily calculated, it is also the least relevant number when determining bus performance. In a shared bus system, such as the PCI bus, this number is rarely achieved. To more accurately represent performance, bus *latency* must be taken into account. Devices attached to the bus can incur several types of latency such as read, write, and arbitration latency. The PCI bus helps reduce the affects of latency by allowing devices to transfer data in *burst mode*. While increasing the length of the burst increases device bandwidth, minimizing the effect of the initial read or write latency, it also increases the latency for other devices waiting to access the bus.

To estimate a device's maximum available bandwidth, it was previously shown in [15] that each device incurs a certain amount of overhead, ov(d), which is proportional to the transaction's burst size *d*. Therefore, the *sustained bandwidth* of one device irrespective of other devices can be calculated by:

$$bw_{sus} = \frac{d}{d + ov(d)} * bw_{pci}$$

(1.1)

If other devices wish to access the bus while it is currently in use, then the device incurs a certain amount of arbitration latency. If there are *n* devices attached to the bus, all needing access, then while one device is granted access to the bus, there are n - 1 devices that must wait. If we assume a round-robin arbitration scheme, then the worst case latency  $\tau_{tat}$  for *n* devices, as shown in [15], can be given by:

$$\tau_{lat} = (n-1)(d + ov(d))$$

(1.2)

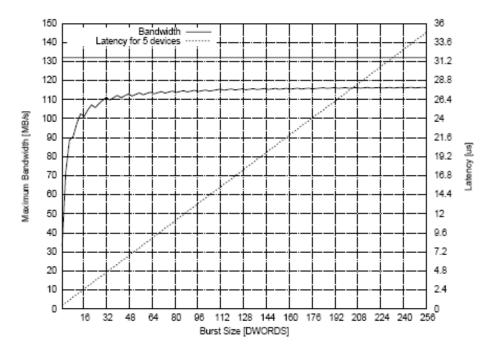

In Figure 1.1 we show the relation between the burst size and the maximum available bandwidth which is shared amongst all devices. It also shows the linear relation between the burst size and the worst-case latency to access the bus when 5 devices are attached.

Most PCI transactions are reads from main memory or writes to main memory, thus making up the majority of overhead. However, simulators usually do not explicitly account for latency due to memory reads or writes. In our research, only one functional simulator handled latency in a dynamic fashion [14]. Depending on the type of latency, such as a read or write, the simulator would assign a range of typical latency values. When calculating the latency, a probability would be assigned to each value within the range. For example, a range of 8 to 12 latency cycles would be assigned when reading from memory, each with equal probability.

Figure 1.1: Relation between burst size and both latency and maximum bandwidth

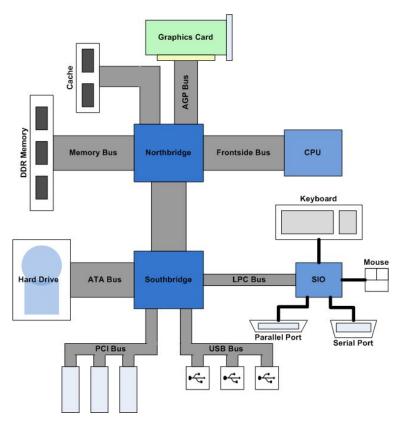

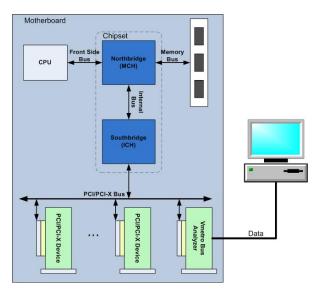

In modern PC systems, *memory bus* bandwidth is shared amongst all processors and devices that access main memory. The system's *Northbridge*, typically known as the Memory Controller Hub (MCH), helps control access to system memory while also controlling access to the various other buses attached to it. The system's processors attach to the Northbridge via the *frontside bus*. To prevent performance bottlenecks, the frontside and memory bus should, and usually does, provide the highest bandwidth in the system. The system's Southbridge, also known as the I/O Controller Hub (ICH), acts as a hub to route traffic from typically slower peripheral I/O devices. A typical PC architecture is shown in Figure 1.2.

This thesis will attempt to define the affects of bandwidth and latency on the PCI bus with respect to the behavior of other devices. We use statistics gathered from a PCI analyzer tool, VMETRO's Vanguard PCI Bus Analyzer [19], to provide real-world results which are used to support our conclusions. From this we can build an accurate software PCI simulation tool based on ScriptSim. In addition, we support a fullyfunctional web interface which allows the designer to quickly set-up and run simulations. The interface will allow full control over various parameters as well as various analysis tools.

Figure 1.2: Modern PC architecture

# 1.2 Contributions

Our main contributions in this thesis include:

• The development of a behavioral PCI simulator. While ScriptSim accurately models functionality as defined by the PCI local specification, it does not model how specific devices affect bus performance. We develop an approach which modifies ScriptSim to allow for behavioral simulation.

- The integration of PCI-X functionality into a PCI simulator. Currently, we know of no behavioral simulators that include PCI-X. Most commercial simulators do include PCI-X functionality, but are used for verification. The inclusion of PCI-X functionality is an important feature since most PCI-X offers significant benefits and has been widely implemented.

- The development of a web-based graphical user interface, PCI Web Sim, for ScriptSim. PCI Web Sim is built on the popular Java Enterprise Edition architecture which features a robust and scalable infrastructure. This interface allows users to perform many important functions relating to PCI simulation including the ability to adjust key performance parameters. Simulations may also be stored in a relational database and various tools can be used to analyze the resulting data.

## 1.3 Synopsys

This thesis is structured as follows. The next chapter describes a historical abstract as well as a current look at bus architectures. Chapter 3 presents related work. In Chapter 4 we describe the PCI bus providing a synopsis of the protocol and important characteristics. In Chapter 5 we extend the thesis to describe the PCI-X standard which includes additions and changes from PCI. Chapter 6 analyzes ScriptSim, the basis of our PCI software simulator. In Chapter 7 we discuss our novel approach to PCI simulation. Chapter 8 provides a look at future uses and contributions. Finally, Chapter 9 provides a conclusion and future work involved.

#### **CHAPTER 2**

#### **CURRENT BUS SYSTEMS**

Computer busses are widely used in systems to connect several peripheral devices together. While some devices are connected using a daisy chain topology (e.g.: SCSI) or via a switched hub as in the case of USB, most modern systems employ a multidrop bus (MDB) topology. A MDB allows devices, which are usually perpendicularly plugged into a connector on the circuit board, to share the same set of electrical wires. Since multiple devices may need to communicate over the bus, an arbiter must be employed to determine which device can use the bus and for how long. Also, a priority scheme may be employed allowing devices with greater need to access the bus before other devices.

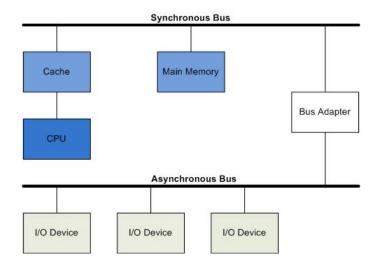

Bus designs can be classified by two different control mechanisms – synchronous and asynchronous. Synchronous busses are used where maximum performance is needed, such as the local (memory) bus but at a cost on inflexibility since increasing the bus speed may cause devices to fail. Asynchronous bus designs are favored because of their flexibility allowing older devices to be used on newer and faster bus systems. However, this price comes at a cost of increased complexity and generally lower performance. Thus, modern computer systems employ both types of buses as illustrated in Figure 2.1. In a computer system, the synchronous bus is noted as the *local bus*, and the asynchronous bus is noted as the *external bus*. This design provides optimum performance for the path between the CPU and memory since this is what mainly determines the overall performance.

Isolating the CPU allows increases in speed to become unhindered. However, the rate at which CPUs and memory increase their speed is faster than the buses that interconnect them. As a result, slow buses left many systems starved for data. In addition, high-bandwidth devices such as video cards were quickly outrunning newer bus systems.

Figure 2.1: Modern computer system which uses both synchronous and asynchronous buses

The remainder of this chapter is structured as follows. In Section 2.1, we describe a variety of alternative bus systems such as the Industry Standard Architecture, VersaModule Eurocard Bus, FutureBus and FutureBus+, InfiniBand, Universal Serial Bus, IEEE-1394 or Firewire, Accelerated Graphics Port, and Peripheral Component Interconnect Express.

#### 2.1 Bus Systems

In this section we present a brief overview of a variety of bus systems along with their architecture and design principles. These buses provide a historical perspective which may have influenced the design of the PCI bus. We also look at some buses that proceeded PCI for completeness. In Table 2.1, we summarize the various bus systems discussed in the following sections.

#### 2.1.1 Industry Standard Architecture Bus

The *Industry Standard Architecture* [1] (ISA) bus originally started out as an 8-bit bus system in 1981 for the IBM PC. Dubbed the XT architecture, it was later extended to a 16-bit data path in 1983 and was renamed to the AT bus architecture after the IBM AT. The maximum transfer rate of 8.3 MB/s at 8.3 MHz in the original version was reasonable enough for low bandwidth requirements. Every transaction is actively controlled by either the CPU or a single direct memory access (DMA) controller which synchronize their bus accesses using a direct wire. While the ISA protocol allows for bus masters, the devices are "passive" in that they cannot actively request the bus and transfer data to main memory autonomously. This allows the bus to operate without an arbiter. In order to transfer data, devices could be programmed to announce the availability of data to the DMA controller which then would perform the transfer without the interaction of the CPU. The proliferation of high bandwidth applications has rendered ISA virtually extinct in modern computer systems.

| Bus Name           | Width<br>(bits) | Frequency (MHz) | Max. Bandwidth (MB/s) |

|--------------------|-----------------|-----------------|-----------------------|

| ISA                | 8 / 16          | 8.3 / 8.3       | 8.3 / 16              |

| EISA               | 32              | 8.3             | 33.2                  |

| VLB                | 32              | 33              | 132                   |

| PCI                | 32              | 33              | 132                   |

| PCI 2.1            | 64              | 66              | 528                   |

| PCI-X 1.0          | 64              | 133             | 1,064                 |

| PCI-X 2.0 (mode 1) | 64              | 133x2           | 2,128                 |

| PCI-X 2.0 (mode 2) | 64              | 133x4           | 4,256                 |

| AGP                | 32              | 66              | 264                   |

Table 2.1: Comparison of various common bus systems (continued on pg. 10)

| AGP (x2 mode)      | 32          | 66x2            | 528                      |

|--------------------|-------------|-----------------|--------------------------|

| AGP (x4 mode)      | 32          | 66x4            | 1,056                    |

| USB 1.0            | 1 (serial)  | N/A             | 0.185 (sync) 1.5 (async) |

| USB 2.0            | 1 (serial)  | N/A             | 60                       |

| Firewire/IEEE-1394 | 1 (serial)  | N/A             | 400                      |

| FutureBus          | 32          | 100             | 400                      |

| FutureBus+         | 256         | 100             | 3,200                    |

| VMEbus             | 64          | 10 (100ns cycle | 80                       |

|                    |             | time)           |                          |

| PCI Express (x1)   | 1 (serial)  | 2,500           | 400                      |

| PCI Express (x2)   | 2 (serial)  | 2,500           | 800                      |

| PCI Express (x4)   | 4 (serial)  | 2,500           | 1,600                    |

| PCI Express (x8)   | 8 (serial)  | 2,500           | 3,200                    |

| PCI Express (x16)  | 16 (serial) | 2,500           | 6,400                    |

| I CI LAPICOS (AIO) | 10 (berrar) | 2,000           | 0,100                    |

Table 2.2: Comparison of various common bus systems (continued from pg. 9)

## 2.1.2 VersaModule Eurocard Bus

The *VersaModule Eurocard* [2] (VME) is an asynchronous, master-slave, parallel bus which was developed in the late 1970's and based off the architecture of the VERSAbus. The VERSAbus architecture featured a 16-bit data path and 24-bit address and was later renamed VME which expanded the data path to 32 bits and supported transfer rates of up to 40 MB/s. An enhancement to VME, named VME64, extended support to 64-bits and provided transfer rates of 80 MB/s. Later versions of the VMEbus (2eSST) could achieve sustained throughput of 1GB/s.

Every VMEbus must contain a system controller to perform arbitration via the arbitration bus. The system controller resides in slot one of Eurocard chassis and the functionality provided is independent of the physical card which resides in the slot. In other words, a master or slave may exist along with the system controller in the same slot. The VMEbus allows for three arbitration modes: *fixed-priority mode* (PRI), *round-robin* (RR), and *single level* (SGL). The arbitration mode is selected during initialization of the system and cannot by changed while the system is running. Each arbitration mode offers four bus request levels (BRL) giving highest priority to level three and lowest to level zero. Devices that are at the same level will be granted bus access dependent upon the proximity to slot one. Fixed-priority arbitration arbitrates between all four levels granting access to the highest priority device first. Round-robin grants bus access sequentially giving all four levels equal access. In single level mode, arbitration only occurs in BRL 3 while all other levels are ignored. VMEbus also allows for a mix of PRI and RR modes.

The VME system supports a wide range of microprocessors including the Motorola 680X0, SPARC, ALPHA, and the x86. It is most widely used in high performance multiprocessor servers and embedded systems such as factory automation, in-flight video servers, avionics, and cellular-phone base stations, as well as many others.

#### 2.1.3 FutureBus / FutureBus+

*FutureBus*+ [3, 4] is described as a high-performance asynchronous bus which improved on the original *FutureBus* design. Work on FutureBus first started in 1979 and was seen as a replacement to the VMEBus. In the following years, complexity of FutureBus grew, slowing down the standardization process. It wasn't until 1987 that an agreement was made on the FutureBus standard which was published as IEEE 896.1-1987.

Shortly after the announcement of the FutureBus standard, the U.S. Navy selected FutureBus+ for its Next Generation Computing Resources. The architecture of FutureBus+ is processor independent and can support bus widths of up to 256 bits. Arbitration of the bus can either be *centralized* or *decentralized*. Each FutureBus+ module carries with it a unique 8-bit arbitration number. When requesting bus access, the module with the highest number is granted access as determined by the arbitration logic. Data transfers are burst oriented – the address is first sent followed by the entire data burst.

Unfortunately, in the end, very little use was made of FutureBus. However, the development strongly influenced the development of other bus systems and provided some of the original work performed on cache coherency.

## 2.1.4 InfiniBand Architecture

The *InfiniBand Architecture* [12] (IBA) specifies a "first order interconnect technology" which describes a system for connecting processor and I/O nodes forming a system area network. The InfiniBand architecture is independent of both the host operating system and processor platform.

Originally named *System I/O*, InfiniBand was the result of merging two competing designs: *Future I/O* and *Next Generation I/O*. InfiniBand was seen as a comprehensive replacement for datacenter I/O including PCI, Fibre Channel, and various other networks. Technically, InfiniBand is based on a switched fabric, point-to-point bidirectional serial communications link intended to connect processors with high-speed peripherals. The serial connection allows for a signaling rate of 2.5 Gbps in each direction. Support for double and quad data speeds are also available offering 5 Gbps and 10 Gbps of data

throughput respectively. InfiniBand is similar to ATM networks in that a certain amount of bandwidth is reserved per connection. It is the responsibility of the switch fabrics to guarantee and enforce bandwidth reservations.

As of today, InfiniBand is used mostly in computer clusters or supercomputers such as the low-cost System X and Cray XD1.

## 2.1.5 Universal Serial Bus

The Universal Serial Bus [5] (USB) is a serial bus standard designed to allow plug-andplay capability while overcoming other known issues such as inflexibility, limited scalability, and extensibility. USB is built upon a well-defined interface for both hardware and software interconnections. This allows new devices to be easily integrated into current systems. With USB-1, bandwidth of 12Mbps was provided for asynchronous transmission, while a rate of 1.5Mbps could be achieved using synchronous data transmissions. USB-2 extends bandwidth capability to 480Mbps to support higher performance systems able to process large amounts data. Devices are classified based on their bandwidth: *low-speed* (10-100kbps), *full-speed* (500kbps-10Mbps), and *high-speed* (25-480Mbps).

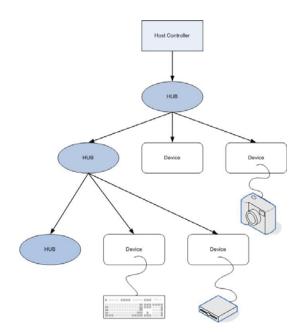

The USB design is asymmetric consisting of multiple daisy-chained peripheral devices connected point to point to a hub device. Adding additional hubs to the chain allows for building a hierarchy as shown in Figure 2.2.

Figure 2.2: USB device hierarchy

Individual devices are referred to as *functions* in USB terminology since each device may host one or more functions, such as webcam with microphone. Transfers of data are based on *pipes* (logical channels) and connect from the USB host controller to an endpoint. Each pipe is unidirectional and holds information about the transfer type and stream requirements. USB provides three types of data transfers: control transfer, interrupt-data transfer, bulk-data transfer, and isochronous-data transfer. Control transfers are used to support configuration information when the device is attached to the bus as well as command and status information. Interrupt transfer is intended for low latency devices that require reliable delivery of data, such as mice and keyboards. Bulk transfers are used for devices that generate of consume large and bursty data, such as printers and scanners. Isochronous transfers are mostly used for time-dependent or real-time information, such as telephony and multimedia streams. USB guarantees the bandwidth for the transfer and provides a bounded latency; both are negotiated prior to the isochronous transfer.

#### 2.1.6 IEEE-1394 Serial Bus / FireWire

*FireWire* [6, 7, 8], also known as *iLink*, is the standard as described in *IEEE-1394* – a composite of documents including *IEEE-1394*, *IEEE-1394a*, and *IEEE-1394b*. Originally created by Apple in 1990, FireWire provides high-speed communication and asynchronous real-time data transfers targeting devices such as video cameras, audio devices, and other peripherals. FireWire can connect up to 63 devices in an acyclic topology allowing peer-to-peer device communication.

There are two current standards of FireWire: FireWire 400 and FireWire 800 (IEEE-1394b). FireWire 400 supports transfer rates of 100, 200, and 400Mbps. FireWire 800, introduced by Apple in 2003, supports a transfer rate of 786.432Mbps and backward compatibility with FireWire 400.

Addresses in FireWire are 64-bits in length and consists of a 10-bit network ID, 6-bit node ID, and 48 bits for memory addressing within each node. Thus, 1023 networks or buses, each with 63 devices, can be supported. Since memory is addressable from every point in the acyclic topology, device connectivity is truly peer-to-peer.

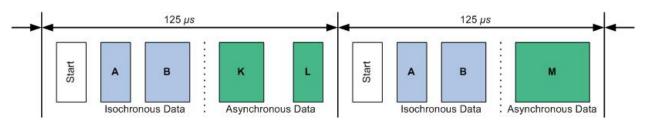

Figure 2.3: IEEE-1394 bus cycle with isochronous and asynchronous data

FireWire defines both the mechanical and timing constraints for arbitration and, unlike PCI, also defines the arbitration scheme. Technically, both FireWire and USB are similar in their technical design construction. The bus is divided into separate time frames each of  $125 \,\mu$ s in length as shown in Figure 2.3. Up to 80% of the bandwidth may be reserved for isochronous data streams, ensuring bandwidth guarantees, while the rest is available for asynchronous data. In between each data packet is a variable-length gap essential for arbitration and maximum propagation delay. These gaps are required to allow bus participants to recognize a packet end since each packet is of variable length.

#### 2.1.7 Accelerated Graphics Port

The *Accelerated Graphics Port* [9, 10] (AGP) is a high-speed point-to-point connection between a graphics card controller and the systems main memory. AGP is targeted at 3D graphical display applications; primarily to improve performance. As of this writing, AGP is currently being phased out in favor of PCI Express.

The AGP specification, in general, is based on the 66MHz PCI specification yet provides significant performance enhancements such as deeply pipelined memory, and demultiplexing of address and data on the bus. By allowing data transfers on both the

rising and falling edge of a clock cycle, transfer rates are twice that of PCI. Also, a new low voltage electrical specification allows four data transfers per 66-MHz clock cycle.

By providing significant bandwidth improvement between the graphics controller and system memory, some of the data structures used for 3D rendering may be effectively moved into main memory. Texture data are well suited for a shift to main memory since they are typically read-only and thus do not have special access ordering or coherency problems. The point-to-point connection of the AGP bus allows guaranteed bandwidth and elimination from bus contention.

However, contention may arise in the host bridge which connects AGP, PCI, and other outside connection to the system memory bus.

Intel's first version of AGP in 1997, titled "AGP specification 1.0," included both the 1x and 2x speeds. Since then, two additional AGP specifications were detailed: specification 2.0 documented AGP 4X and 3.0 documented 8X. The various AGP versions as well as some of the features are outlined below:

# AGP 1x

- 32-bit channel operating at 66 MHz

- Maximum data rate of 266 megabytes per second (MB/s), doubled from the 133 MB/s transfer rate of PCI bus 33 MHz / 32-bit

- 3.3 V signaling.

#### AGP 2x

- 32-bit channel operating at 66 MHz double pumped to an effective 133 MHz

- Maximum data rate of 533 MB/s

- Signaling voltages the same as AGP 1x

## AGP 4x

- 32-bit channel operating at 66 MHz quad pumped to an effective 266 MHz

- Maximum data rate of 1066 MB/s (1 GB/s)

- 1.5 V signaling

# AGP 8x

- 32-bit channel operating at 66 MHz, strobing eight times per clock, delivering an effective 533 MHz

- Maximum data rate of 2133 MB/s (2 GB/s)

- 0.8 V signaling.

### 2.1.8 Peripheral Component Interface Express

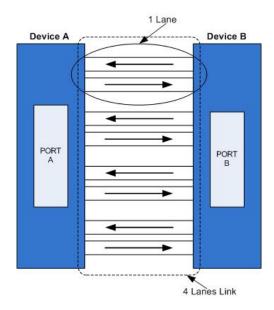

The *Peripheral Component Interface Express* [11] (PCIe) bus is a full duplex point-topoint connection between device card and motherboard. In order to meet higher bandwidth requirements, Intel first expanded PCI to increase the bus width to 64 bits and increase the clock rate to 133MHz. However, increasing the clock speed led to stricter timing requirements and reduced bus slots. In realizing PCI was reaching its upperbounds, in late 1990, Intel began work on its third generation I/O (3GIO) which later became known as PCIe. PCIe is designed as a replacement for PCI, PCI-X, and AGP interfaces. In contrast to PCI, PCIe uses a shared switch instead of a shared bus where each device in the system has direct and exclusive access to the switch. Thus, each device has its own dedicated bus, which is called a *link*. Each link is built around dedicated unidirectional, point-to-point connections known as *lanes*. An example of which is shown in Figure 2.4. A lane consists of a transmit (T) and receive (R) *low voltage differential signal* (LVDS) pair each at 2.5 Gbps. This is in contrast to PCI, where all devices share the same bidirectional, 32-bit (or 64-bit), parallel bus.

Figure 2.4: Two PCIe devices connected by a link consisting of 4 lanes

PCIe is built using a layered protocol similar to that of the IEEE 802 model of computer networking. The protocol consists of:

• *Transaction Layer Protocol* (TLP) – This layer transports read and write requests in the form of packets. The transaction layer supports both 32-bit and 64-bit addressing as well as PCI memory, I/O, and configuration address space. Similar to PCI-X, PCIe implements split transactions which allow the link to carry other traffic while the

target device gathers data for the response. PCIe also utilizes credit-based flow control allowing for quality of service (QoS).

- *Data Link Layer* Adds sequencing of TLP packets generated by the Transaction Layer, 32-bit error detection cyclic redundancy codes (CRC) to the data packets, and an acknowledgement protocol (ACK and NAK signaling) to create a reliable data transfer mechanism.

- *Physical Layer* (PHY) Implements the PCIe link which is built using a collection of

or more lanes. All devices minimally support a single-lane (x1) link and may

optionally support wider links of 2, 4, 8, 12, 16, or 32 lanes. PCIe data transmitted on

multiple links is interleaved, which is known as data striping, and significantly

increases the throughput.

As of today, PCI Express is starting to become the de-facto backplane standards on personal computers. The main reason is its design transparency transparent to software developers; operating systems designed for PCI can boot in a PCI Express system without any modification to the code.

#### **CHAPTER 3**

#### **RELATED WORK**

Work related to PCI simulation is very rare and in most cases not the focal point of previous research studies. To our knowledge, only two papers focus on PCI simulation [14] [15], and only [14] provides implementation details. However, for comparison purposes, we describe two papers that discuss JSIM, a java based simulator.

The remainder of this chapter is structured as follows. In Section 3.1, we discuss PCI Bus modeling, summarized from Chapter 6 of [15]. This provides a basis for calculating worst-case calculations of bandwidth and latency. Section 3.2 describes simulation software, including a PCI Simulator written in C++.

#### **3.1 Using PCI-Bus Systems in Real-Time Environments**

Schönberg's thesis [15] analyses and tries to predict what affect the load of the PCI-bus has on execution times of applications. While the thesis focuses primarily on real-time capabilities of the PCI bus, it provides us with an in-depth analysis of the PCI bus and details a unique method of calculating bandwidth and latency. In addition, we borrow ideas from his mathematical approach to model devices and implement them into our simulator.

#### 3.1.1 Simplified PCI-Bus Model

While PCI simulation aims to provide approximations of real-world results, in some cases worst-case performance may also be useful. In Section 4.2 in [15], Schönberg

presents a unique way to model the behavior of the PCI bus allowing us to calculate worst-case bandwidth and latency. Schönberg does reference a PCI simulation tool, "PCItrace", which was developed to test the performance of various arbitration schemes and arbiters. However no implementation details were provided, and thus, we decided to focus on the modeling aspect described in this section.

To characterize bus transactions, the author presents a simple state model that describes transitions from one bus state to a subsequent state given possible states of the bus. There are four possible states defined regardless of the type of transaction:

**Idle:** The idle state defines the bus to be unused by any device. During this state, no data is being transferred and device requests to access the bus are immediately granted. At least two cycles of latency are needed before the address is transmitted since arbitration is not hidden in the idle state.

**Busy:** The busy state indicates that the bus granted access to a device and is performing an address or data transfer. Wait states are added if either the initiator or target cannot accept or deliver data. This state does not define how the bus is being used, only that is in use.

**Busy/Data:** This state represents the bus is currently busy and it is known that data is transferred.

**Busy/Non-Data:** This state represents the bus is currently busy, however, it is known that no data is transferred (i.e.: address or stalling cycle).

Based on the states described, device behavior can be represented by descriptor D:

$$D = (s, d, r) \tag{3.1}$$

Where *s* defines a *non-data phase*, *d* defines a *data phase*, and *r* defines the *recovery phase*. The recovery phase is not a physical bus phase and only guarantees that devices do not access the bus during this time. Using the device descriptor provides a basis to determine upper bounds for bandwidth and latency when arbitrary devices interact.

Our simulator also defines the notion of a descriptor; however, we decompose it into a master and target descriptor, each having different parameters. It should also be noted that we provide a strict definition of recovery period, which is defined in Section 7.1.1.1.

## **3.1.2** Model for Identical Devices

Before describing the behavior of arbitrary devices, the author first presents a model for n identical devices. The term "Identical Devices" defines all devices which can be described by the same device descriptor D.

The worst-case latency,  $\tau_{lat}$ , occurs when one device must wait all other devices are granted bus access and is given by:

$$\tau_{lat} = (n-1)(s+d)$$

(3.2)

Thus, the worst-case bandwidth occurs when every access to the bus is delayed by this amount and is calculated by:

$$bw = bw_{pci} \frac{d}{(s+d+r) + ((n-1)(s+d) - 1)}$$

(3.3)

There are two cases which must be considered depending on the length of the recovery phase. It is noted that each device is assumed to operate at its maximum bandwidth (i.e.: there are no gaps between two requests).

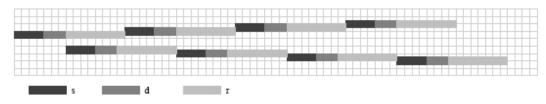

1. In the first case,  $r \ge (n-1)(s+d)$  and thus a device can access the bus immediately following the end of its recovery phase. Figure 3.1 illustrates an example of for two devices.

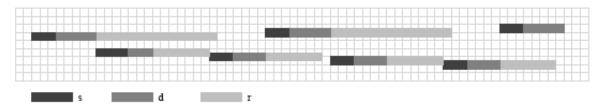

Figure 3.1: Two identical devices with D = (4, 3, 8)

It must be noted that each device has the same recovery length and thus it is not possible for a device to perform multiple transactions while another device recovers.

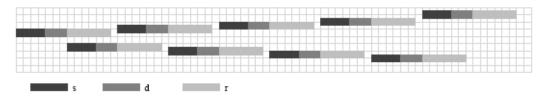

2. In the second case, r < (n-1)(s+d) and thus a device is ready before all other devices have finished their transaction. Figure 3.2 illustrates this example.

Figure 3.2: Two identical devices with D = (4, 3, 6)

The combination of both cases can be used to calculate the bandwidth each device can achieve by:

$$bw = bw_{pci} \frac{d}{\max((s+d)n, (s+d+r))}$$

(3.4)

The two cases above can also be used to calculate the bus utilization, U(n), for n active devices. The bus utilization is defined by the ratio of the number of cycles where the bus is occupied and the number of elapsed bus cycles which is calculated by:

$$U(n) = \frac{(s+d)n}{\max((s+d)n, (s+d+r))}$$

(3.5)

From Equation 3.4, the bandwidth generated by n devices, where each device sends at its maximum rate is calculated by:

$$bw(n) = bw_{pci} \frac{dn}{\max((s+d)n, (s+d+r))}$$

(3.6)

Therefore, the bandwidth of a system with a single device is calculated by bw(1). If r is set to zero and s is set to the overhead, ov(d), then Equation 1.1 is realized. It must be noted that the minimum value of s during a read is 2 (address plus turn-around cycle), while the minimum value for a write is 1 (address cycle). Arbitration does not require an extra cycle under high bus load since arbitration is hidden.

Finally, the maximum number of devices that can be connected to the bus,  $n_{max}$ , where each device can send at its maximum possible bandwidth is calculated by:

$$n_{\max} \left\lfloor \frac{r}{s+d} \right\rfloor + 1 \tag{3.7}$$

### 3.1.3 Model for Arbitrary Devices

Modeling a PCI system with identical devices employs an ideal situation. In real-life, devices have different properties and perform varying functionality. Thus, the values of our device descriptor s, d, and r may vary which might not cause the neat interleaving caused by modeling identical devices. Overall bus utilization is less than theoretically possible since it is less than the sum of the individual device's utilization. The author

models this problem from Liedtke *et al.* [20] and proposes a new technique which we summarize in this following section.

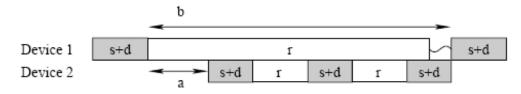

Figure 3.3: Two sample devices with  $D_1 = (4, 3, 6)$  and  $D_2 = (3, 4, 7)$

Figure 3.3 illustrates two arbitrary devices where one device can perform multiple transactions while the other device recovers. The following paragraphs develop models for two devices and then generalize for multiple devices.

### 3.1.3.1 Two Devices

Given two devices with descriptors  $D_1$  and  $D_2$ , in order for  $D_2$  to perform multiple transactions, the following must hold:

$$s_2 + d_2 + r_2 < r_1 \tag{3.8}$$

Therefore it is shown that  $D_2$  can at least start another transaction while  $D_1$  has yet to finish its recovery phase. It is assumed that  $s_1 + d_1 + r_1 \ge s_2 + d_2 + r_2$ . The *displacement* of  $s_2 + d_2$  in relation to  $s_1 + d_1$  is denoted by *a*:

$$a \in [0, r_2 - (s_1 + d_1)] \tag{3.9}$$

Where  $r_2 - (s_1 + d_1)$  returns 0 when  $s_1 + d_1 > r_2$ .

The *block time* (*b*) is defined as the distance between two starts of  $D_1$  at  $s_1 + d_1 > r_2$ which depends on the displacement (*a*) between the end of the transaction of  $D_1$  and the start of the transaction of  $D_2$  by b = b(a). The number of transactions  $D_2$  can perform with length  $s_2 + d_2$  during the interval  $[s_1 + d_1 + a, s_1 + d_1 + r_1)$  is denoted by v = v(a).

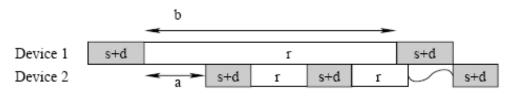

Figures 3.4 and 3.5 illustrate two cases, explained below, where the second device  $D_2$  can perform at least two (possibly more) transactions during the recovery phase of  $D_1$ . It is of note that ~ represents a period of time no data can be transferred since it is in use by another device.

Figure 3.4: Two devices, multiple transactions, with delay

Figure 3.5: Two devices, multiple transactions, without delay

The following are the two cases to be considered:

1. In Figure 3.4,  $D_2$  started its last transaction but it exceeds the recovery phase of  $D_1$ . Thus, D1 must wait until  $D_2$  finishes its final transaction.

2. In Figure 3.5, the last work phase of  $D_2$  is shorter than the recovery phase of  $D_1$ . Thus,  $D_1$  is granted immediate access to the bus since  $D_2$  is in its recovery phase.

The number (v) of transactions that can be performed by  $D_2$  during the recovery phase of  $D_1$  is calculated by:

$$\max\{v \mid r_{1} > (v-1)(s_{2} + d_{2} + r_{2}) + a_{i}\}$$

$$v-1 < \frac{r_{1} - a_{i}}{s_{2} + d_{2} + r_{2}} \text{ with } r_{1} > a_{i} \ge r_{2}$$

$$v = \left\lceil \frac{r_{1}}{s_{2} + d_{2} + r_{2}} \right\rceil$$

(3.10)

By setting  $a_0 = 0$ , the block time  $b_i$  and the displacement time  $a_i$  is calculated by:

$$b_{i} = s_{1} + d_{1} + \max(r_{1}, (v_{1} - 1)(s_{2} + d_{2} + r_{2}) + a_{i-1} + (s_{2} + d_{2}))$$

$$a_{i} = a_{i-1} + v * (s_{2} + d_{2} + r_{2}) - b_{i}$$

(3.11)

While Equation 3.11 calculates how often a device is scheduled, there is no closed formula to determine the exact bandwidth and latency. It should be noted that the worst-case latency for  $D_1$  is  $\tau_{lat,1} = s_2 + d_2$  and for  $D_2$  is  $\tau_{lat,2} = s_1 + d_1$ .

### 3.1.3.2 Multiple Devices

The number of access combinations can be easily described by the formulas given in the previous section. However, this number increases polynomially with an increasing number of devices. In most cases it is sufficient to know the worst-case bandwidth latency. To obtain the formula for worst case latency, it must be assumed that exactly one cycle before the recovery phase of device *x* ends, all other devices request the bus and the first device is chosen per the round-robin arbitration scheme. The worst-case latency when all *n* devices receive the bus for  $s_i + d_i$  cycles for device *x* is given by:

$$\tau_{lat,x} = \sum_{i=1, i \neq x}^{n} (s_i + d_i) - 1$$

(3.12)

Using Equation 1.1, the bandwidth a device can achieve can be calculated by:

$$bw_x = \frac{d_x bw_{pci}}{s_x + d_x + r_x + \tau_{lat,x}}$$

(3.13)

Therefore, combining Equation 3.12 with 3.13 will result in the worst-case bandwidth of device *x*:

$$bw_{x} = \frac{d_{x}bw_{pci}}{s_{x} + d_{x} + r_{x} + \left(\sum_{i=1, i \neq x}^{n} (s_{i} + d_{i}) - 1\right)}$$

(3.14)

### 3.1.4 Concluding Remarks

This paper provided a unique look at modeling the PCI and providing equations to calculate worst-case bandwidth and latency. One of the key aspects of our simulator is the notion of recovery period, which was borrowed from the author's work as well as the idea of a descriptor. However, our simulator divides the descriptor into a master and target device descriptor, each with its own set of parameters. In addition, the authors work aided us in describing results obtained in our simulator, specifically in Section 8.2. To verify the results, the author used the PCI Pamette [21] and custom software to generate PCI cycles and analyze the results.

## **3.2** Simulation Software

This section analyzed three papers on simulation software. While only the last paper describes a PCI simulator, we discuss two other software-based simulators that are analyzed and evaluated.

## 3.2.1 JSIM: A Java-Based Simulation and Animation Environment

A Java-based simulation and animation environment, JSIM, is described in [25]. JSIM is a collection of java classes, which are grouped into five library packages (queue, statistic, variate, process, and event) that can be extended by a user to model complex simulations. As an example, the authors created a simple M/M/1 Bank simulation model utilizing the JSIM simulation library. The concept of the simulation library is built around graph theory, representing models as directed graphs with varying node types. To minimize the amount of coding needed to create a simulation, a graphical design environment was implemented which allows users to model simulations using point and click operations. However, one of the key features is the ability to recall previous simulation results based on information of the current simulation. This approach, described as Query Driven Simulation (QDS), significantly reduces simulation times and cost by retrieving simulation results that were previously stored.

JSIM is a generic simulation environment which does not model any one particular system; in contrast our simulator only models PCI/PCI-X systems. However, it provides us with insight on implementation details contrasting it with our approach. Our implementation will also use Java; however, we use it only as a middle-tier framework that connects to the simulator and database. Our design also stores detailed information about the simulation in a database, however, it is not query driven. Instead, the user can manually recall previous run simulations and review the results. While both the JSIM design and our design provide a graphical user interface, our design requires no user coding and does not need to be installed onto the user's PC.

#### 3.2.2 Building a Web-Based Federated Simulation System with Jini and XML

In Huang and Miller [26], a collaborative approach to building and running complex distributed simulation models based on JSIM is explored. The design is based on the High Level Architecture (HLA) developed by the Department of Defense (DoD). It defines the concept of a federation – a simulation system built from components called federates. Early implementations of JSIM involved using Enterprise Java Beans (EJB) [27]; however, its thin-client/thick-server oriented design was deemed an imperfect solution for HLA-style simulation systems. The authors found a solution in Jini [28], a set of API's and protocols that allow the development and deployment of distributed

systems organized as a federation of services rather than a central controller like EJB. These services form a peer network made available via a lookup service. The looselycoupled architecture allows objects to be deployed, removed, and relocated without the need to redeploy the entire system. Object mobility is easily obtained through the use of Remote Method Invocation (RMI), allowing services to communicate through the network.

While Jini allows simulation models and model agents the ability to collaborate, one obstacle the authors posed was how they would all understand each other. One solution was to use the eXtensible Markup Language (XML) [29] as the carrier of event data. XML is a general-purpose markup language whose primary purpose is exchange structured data across differing systems. To achieve interoperability, the authors propose devising a common Document Type Definition (DTD) defining a simulation schema. By using Jini and XML, the authors' goal is to turn JSIM into a web accessible distributed simulation system. The GUI is presented as a Java Applet with simulation data.

Since this simulation environment is also based on JSIM, we note that it does not simulate any particular system, however it does provide implementation details which are similar to our system. While our implementation is also web-based, we decided to use the EJB architecture to store and retrieve simulation data. This solution was stated by the author [26] to be "very useful for managing simulation data on the database side." Our proposed design uses HTML and JavaScript to render the GUI in a browser in contrast to the Java Applet design proposed by the author.

#### **3.2.3** Design and Implementation of PCI Bus Based Systems

In this section, we summarize a PCI simulator described in Section 7.5 of [14]. The simulator was designed in part to compare results based on modifications of the PCI protocol by the author in order to improve performance and efficiency. The author offers the introduction of the Split Cycle (not to be confused with the Split Cycle introduced by the PCI-X protocol) which allows masters to send read requests to targets. Once the request has been filled by the target, it then uses a normal write transaction to provide data to the original requestor. This method eliminates wait cycles initiated by the target while it waits for the data, thus wasting valuable bandwidth that could be used by other devices.

## 3.2.3.1 Collecting PCI Traffic

In order to accurately model PCI traffic it is necessary to retrieve bus cycles of a typical system. There are three methods identified by the author which would prove to be useful in evaluating our simulator. We briefly describe the three methods in the following sections.

### 3.2.3.1.1 Logic Analyzer

A logic analyzer allows collection of detailed bus cycle information. This information can be analyzed to extract high level information needed for modeling purposes. However, logic analyzers offer limited buffer space and would not accommodate the sheer amount of PCI transactions needed for proper modeling.

#### 3.2.3.1.2 PCI Bus Monitor

A PCI bus monitor allows transactions to be analyzed passively. However, data acquisition is usually stored in raw form which provides additional information that may not be needed. Secondly, the monitor has to be designed such that it can connect to a mass storage device or some other connection for data storage.

#### 3.2.3.1.3 PCI Monitor Card

While the previous two methods looked at collecting transactions on a cycle by cycle basis, another approach is to collect statistics about individual transactions. A PCI monitor card could be attached to the bus loaded with the configuration header of each device attached to the bus. Thus, the monitor would only need to look at the destination address of each transaction to distinguish between PCI transactions. The PCI monitor would collect the following information:

- Average, minimum, and maximum initial latency cycles This can be obtained by measuring the time from FRAME# being asserted until the first data word.

- 2. Average, minimum, and maximum burst latency cycles This is obtained by measuring the number of cycles between consecutive words in a burst transfer.

- 3. Average, minimum, and maximum transfer burst length This is obtained my counting the number of data transfers during a single transaction.

- Average, minimum, and maximum wait states before a retry cycle generation This is obtained by counting the number of wait cycles until a retry cycle appears.

- 5. Average, minimum, and maximum burst length before a retry cycle generation This is obtained by counting the number of data cycles until a retry cycle appears.

35

6. Relative frequency of each base address access and the cycle type (read or write).

Collecting this information gives a good statistical profile for each device which can be used to simulate bus cycles within a simulator. In addition, statistical profiling requires only a fixed amount of memory. Profiling data can be collected almost indefinitely (provided enough memory is set aside).

#### **3.2.3.2 Generating PCI Bus Traffic Simulation**

Generating bus traffic can be based on the transactions cycles as described in the first two methods above, or by the statistical information gathered which would generate random cycles. We note that the author modified the PCI protocol and the transaction data used to generate cycles. The modifications are as follows:

- 1. The modified PCI protocol allows for a new transaction to be started while the previous transaction is being retried, thus simulating the Split Transaction proposed by the author.

- 2. All idle bus cycles are removed since it is necessary to test the efficiency of the protocol and not the chipset.

- Captured transactions are optimized based on PCI optimization rules (byte merging, consecutive word merging). This is also necessary in order to test bus efficiency and not chipset efficiency.

### **3.2.3.3** PCI Simulation Implementation

Implementation of the PCI simulation framework was developed exclusively using C++. While writing the simulator in Verilog was considered by the author, it was ruled out in favor of C++ for the following reasons:

- 1. The cycle based approach used in the C++ simulator yielded simulations times that were orders of magnitude quicker when compared with the Verilog simulator.

- 2. By exploiting class inheritance and object oriented design, C++ allowed for better customization and no duplication.

- 3. Verilog licensing could limit availability.

The simulation is divided into three parts:

- The simulator provides a cycle based library which supports synchronous modules. Each module can contain one or more register objects, storing a single bit, which are connected by wire objects. Both register and wire objects are represented by one of six logic levels: low, high, high-Z, unknown, pull-high, and pull-low.

- 2. The simulator also provides generic models consisting of a PCI arbiter, PCI target, PCI master, PCI backplane, and a PCI monitor. The modules allow for fine grained control over their behavior including master and target burst length, wait states, initial latency, burst latency, and retry generation by a target. Different arbitration schemes may be specified and new ones may be added by the user.

- 3. In addition to the generic models, modified models are also included to allow for support of the proposed enhancements.

#### 3.2.3.4 PCI Simulation Environment

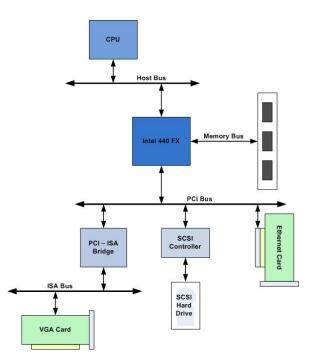

This section outlines the environment used to simulate PCI bus transactions. Instead of using actual transactions, statistics were extracted from the data gathered. The hypothetical system used to perform the simulation is illustrated in Figure 3.6.

The system is based off the Intel 440FX PCI chipset [22] and uses the following data for the simulation:

- For system memory:

- Average initial latency for reads is between 8 and 12 cycles long.

- Average initial latency for writes is between 3 and 4 cycles long.

- No wait states for cache line transfer on 32 byte boundary, and 1 cycle latency for transfers which cross a cache line boundary.

- Burst length up to 4K page boundary. Transfer terminates at a cache line boundary.

- For the CPU:

- Average initial latency for writes to the PCI bus is between 1 and 3 cycles with a burst length of up to 7 words.

- No master initial latency for reads from the PCI bus (1 word per transaction).

- Arbitration:

- Round-robin arbitration scheme.

- Bus granted to next master after current master releases the **REQ**# line, or when the Multi-transaction Timer (MTT) expires.

The system consists of the following PCI devices to be simulated: a target representing system memory, a target representing a VGA card, a master representing a SCSI controller, a master representing an Ethernet card, and a master representing the CPU. The performance characteristics for the system memory and the VGA card are summarized in Table 3.1. Performance characteristics for the Host Bridge, SCSI controller, and Ethernet card are summarized in Table 3.2. The CPU reads directly from the VGA card and will not support bursts. Conversely, the CPU writes directly to the VGA card and bursts are allowed.

Figure 3.6: Hypothetical system used for PCI simulation

| <b>Table 3.1:</b> | Simulation | target | parameters | (continued | on pg. 40)                            | )   |

|-------------------|------------|--------|------------|------------|---------------------------------------|-----|

|                   |            |        |            | (          | · · · · · · · · · · · · · · · · · · · | · . |

| Туре                         | VGA Target       | System Memory Target   |

|------------------------------|------------------|------------------------|

| Decode Speed                 | Medium           | Fast                   |

| Initial Wait States (cycles) | Random (0 to 40) | Read: Random (8 to 12) |

|                              |                  | Write: Random (3 to 4) |

| Burst Wait States (cycles)   | 0                | 32-byte Boundary: 1    |

|                                  |                  | Other: 0            |

|----------------------------------|------------------|---------------------|

| Burst Length (cycles)            | Random (0 to 10) | Stop at 4k Boundary |

| Initial Retry Threshold (cycles) | 16               | 16                  |

| Burst Retry Threshold (cycles)   | 8                | 8                   |

Table 3.2: Simulation target parameters (continued from pg. 39)

A description of each of the target parameters listed in Table 3.1 is provided below:

**Decode Speed**: A target has four possible speeds for asserting **DEVSEL#** after **FRAME#**: fast, medium, slow, and subtractive. A fast target responds within one clock cycle, a medium target within two cycles, and a slow target within three cycles. If no agent claims the transaction within three cycles, then a subtractive-decode agent may claim it on the fourth cycle.

**Initial Wait States**: This is the number of clock cycles before the target is ready to send or receive the first word.

**Burst Wait States**: The number of clock cycles before the target is ready to send or receive burst words, after the first word.

Burst Length: The number of words the target is either able to send or accept.

**Initial Retry Threshold**: A target that has to wait *n* number of cycles can either (1) wait *n* clock cycles with **TRDY#** deasserted and then assert **TRDY#**, or (2) retry the cycle. If *n* is greater than the initial retry threshold, then a retry will be generated, else, wait states

will be added. This only applies to the first word in a burst and is limited to 16 clock cycles per the PCI 2.1 specification.

**Burst Retry Threshold**: Similar to the initial retry threshold, this applies to subsequent burst words and is limited to 8 per the PCI 2.1 specification.

| Туре                       | CPU Host Bridge  | Ethernet Card    | SCSI Controller |

|----------------------------|------------------|------------------|-----------------|

| Read/Write Ratio           | 80/20            | 80/20            | 20/80           |

|                            | (Random)         | (Random)         | (Random)        |

| Initial Wait States        | 0                | 0                | 0               |

| (cycles)                   |                  |                  |                 |

| Burst Wait States (cycles) | 0                | 0                | 0               |

| Burst Length (cycles)      | Read: 1          | Random: 8 to 384 | 128             |

|                            | Write: Random (1 |                  |                 |

|                            | to 8)            |                  |                 |

| Master Latency Timer       | 48               | 48               | 48              |

| (cycles)                   |                  |                  |                 |

| Retry Overhead (cycles)    | 0                | N/A              | N/A             |

| Transaction Count          | 200              | 100              | 100             |

Table 3.3: Simulation master parameters

A description of each of the master parameters listed in Table 3.2 is provided below:

**Read/Write Ratio**: This is the ratio between the percentage of PCI read commands and write commands for this master.

**Initial Wait States**: The number of clock cycles before the master is ready to send or receive the first word.

**Burst Wait States**: The number of clock cycles before the master is ready to send or receive burst data, after the first word.

Burst Length: The number of words the master is either able to send or accept.